QorlQ Qonverge Platform

# QorlQ Qonverge BSC9132 for Picocell Base Station Solutions

## A new dimension in wireless processing

#### Overview

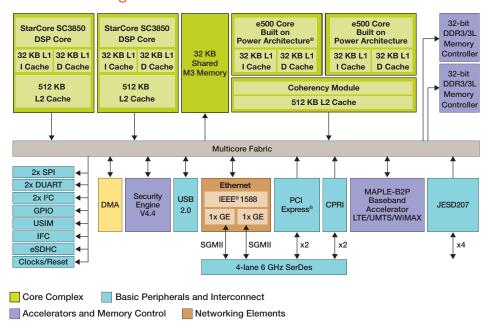

The BSC9132 is a highly integrated device that targets evolving microcell, picocell and enterprise femto base station applications. The BSC9132 device combines two e500 cores, built on Power Architecture® technology, and two StarCore SC3850 cores with MAPLE-B2P baseband acceleration processing elements to address the need for a high-performance, cost-effective, integrated solution that handles all required processing layers without the need for an external device (except for an RF transceiver).

With primary target air interfaces for LTE-FDD/TDD, WCDMA (HSPA+) and WiMAX, the BSC9132 programmable device supports the performance and cost requirements of up to 20 MHz single sector LTE-FDD/TDD by handling 150 Mb/s downlink and 75 Mb/s uplink rates, and 5 MHz HSPA+ by handling 42 Mb/s downlink and 23 Mb/s uplink. The BSC9132 supports multimode operation that enables it to process LTE-FDD/TDD and WCDMA (HSPA+) users simultaneously.

### QorlQ Qonverge BSC9132 Processor

#### **Target Applications**

Picocell: Small cell wireless base stations supporting the following standards:

- LTE-FDD/TDD

- WCDMA (HSPA+)

- TD-SCDMA

- WiMAX

### **QorlQ Qonverge Features**

| The BSC9132 is a highly integrated device combining Power, StarCore and MAPLE architectures. The device includes the following features: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core                                                                                                                                     | Power Architecture technology including two e500 processors with 512 KB shared L2 cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DSP                                                                                                                                      | Two StarCore SC3850 DSP subsystems, each with a 512 KB private L2 cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Baseband Acceleration                                                                                                                    | The MAPLE-B2P multi-accelerator platform engine supports functions that enable LTE-FDD/TDD, WiMAX and WCDMA (HSPA+) wireless standards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Memory                                                                                                                                   | <ul> <li>32 KB of shared M3 memory</li> <li>Two DDR3/3L memory interfaces with 32-bit data width (40 bits including ECC), up to 1333 MHz data rate</li> <li>Integrated flash memory controller</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Security                                                                                                                                 | Dedicated security engine featuring trusted boot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RF Interface                                                                                                                             | Three full-duplex and one half-duplex JESD207 RF interfaces  Two CPRI interfaces for remote radio head integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Connectivity                                                                                                                             | <ul> <li>Two DMA controllers. One with four bi-directional channels and the other with 16 bi-directional channels—one controller serves both the Power Architecture cores and DSP domains with the other controller used mainly for DSP operations.</li> <li>Two triple-speed Gigabit Ethernet controllers featuring network acceleration, including IEEE® 1588 v2 hardware support for two SGMII ports</li> <li>USB 2.0 host and device controller</li> <li>Two DUART, two SPI and two I²C controllers</li> <li>96 GPIO, TDM with 512 channels</li> <li>USIM interface</li> <li>Enhanced Secure Digital Host Controller (eSDHC) interface to MMC, SD and SDIO cards</li> </ul> |

| Interfaces                                                                                                                               | Four-lane SerDes PHY that multiplexes the following:     Two CPRI controller lanes     Two SGMII interfaces     Two PCIe lanes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Freescale will provide comprehensive and commercial L1, L2, L3 and transport software, integrated and tested on BSC9132 platforms:

- LTE-FDD/TDD and WCDMA (HSPA+)

VortiQa L1 baseband software licensed by Freescale

- LTE PHY Conformance (LPC) and Test Toolkit software licensed by Freescale

- L2/L3 software for LTE-FDD/TDD and WCDMA (HSPA+) via partners

- Development tools and operating system software through Freescale and its ecosystem partners

Freescale, the Freescale logo, QorlQ Qonverge and StarCore are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2012–2014 Freescale Semiconductor, Inc.