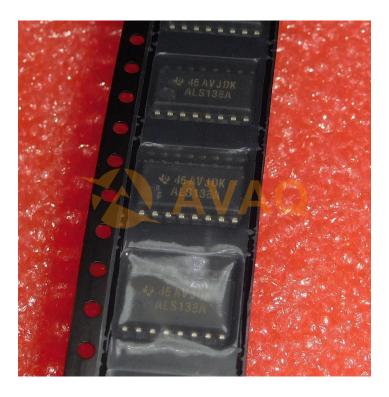

# SN74ALS138ANSR

### Decoder/Demultiplexer Single 3-to-8 16-Pin SOP T/R

Manufacturer: <u>Texas Instruments, Inc</u>

Package/Case: SOP-16

**Product Type:** Logic ICs

RoHS: RoHS Compliant/Lead free RoHS

**Lifecycle:** Active

Images are for reference only

Inquiry

### **General Description**

The 'ALS138A and 'AS138 are 3-line to 8-line decoders/demultiplexers designed for high-performance memory-decoding or data-routing applications requiring very short propagation delay times. In high-performance systems, these devices can be used to minimize the effects of system decoding. When employed with high-speed memories with a fast enable circuit, the delay times of the decoder and the enable time of the memory are usually less than the typical access time of the memory. The effective system delay introduced by the Schottky-clamped system decoder is negligible.

The conditions at the binary-select (A, B, and C) inputs and the three enable (G1,, and) inputs select one of eight output lines. Two active-low and one active-high enable inputs reduce the need for external gates or inverters when expanding. A 24-line decoder can be implemented without external inverters and a 32-line decoder requires only one inverter. An enable input can be used as a data input for demultiplexing applications.

The SN54ALS138A and SN54AS138 are characterized for operation over the full military temperature range of -55°C to 125°C. The SN74ALS138A and SN74AS138 are characterized for operation from 0°C to 70°C.

# **Key Features**

Designed Specifically for High-Speed Memory Decoders and DataTransmission Systems

Incorporate Three Enable Inputs to Simplify Cascading and/orData Reception

Package Options Include Plastic Small-Outline (D) Packages, Ceramic Chip Carriers (FK), and Standard Plastic (N) and Ceramic (J) 300-mil DIPs

#### Description

The 'ALS138A and 'AS138 are 3-line to 8-line decoders/demultiplexers designed for high-performance memory-decoding or data-routing applications requiring very short propagation delay times. In high-performance systems, these devices can be used to minimize the effects of system decoding. When employed with high-speed memories with a fast enable circuit, the delay times of the decoder and the enable time of the memory are usually less than the typical access time of the memory. The effective system delay introduced by the Schottky-clamped system decoder is negligible.

The conditions at the binary-select (A, B, and C) inputs and the three enable (G1, , and ) inputs select one of eight output lines. Two active-low and one active-high enable inputs reduce the need for external gates or inverters when expanding. A 24-line decoder can be implemented without external inverters and a 32-line decoder requires only one inverter. An enable input can be used as a data input for demultiplexing applications.

The SN54ALS138A and SN54AS138 are characterized for operation over the full military temperature range of -55°C to 125°C. The SN74ALS138A and SN74AS138 are characterized for operation from 0°C to 70°C.

# **Recommended For You**

**SN74S38N**

Texas Instruments, Inc

DIP

**SN74F08D**

Texas Instruments, Inc

SOP-14

SN74LS245DW

Texas Instruments, Inc

SOP20

SN7406N

Texas Instruments, Inc

DIP-14

SN74LS14N

Texas Instruments, Inc

DIP

SN7438N

Texas Instruments, Inc

DIP14

SN74LS257BN

Texas Instruments, Inc

DIP16

SN74LS74AN

Texas Instruments, Inc

DIP

SN74CBTLV3257D

Texas Instruments, Inc

SOP-16P

**SN74HC139N**

Texas Instruments, Inc

DIP

SN75462P

Texas Instruments, Inc

DIP8

SN75452BP

Texas Instruments, Inc

DIP8

SN74S74N

Texas Instruments, Inc

DIP

SN74HC138DR

Texas Instruments, Inc

SOP16

SN74AVC16T245DGGR

Texas Instruments, Inc

TSSOP48