**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

Is Now Part of

# **ON Semiconductor**®

To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor dates sheds, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor dates sheds and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use on similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor and its officers, employees, subsidiaries, affliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out or i, directly or indirectly, any lange of the applicatio customer's to unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the

**FAIRCHILD**

## www.fairchildsemi.com

# Application Note AN6032 FAN4800 Combo Controller Applications

### **General Description**

This application note shows the step-by-step process to design a high-performance supply. The equations shown in this document can also be used for different output voltages and total power.

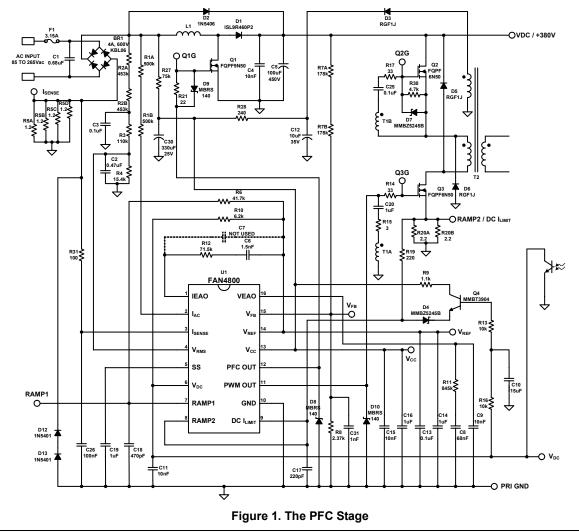

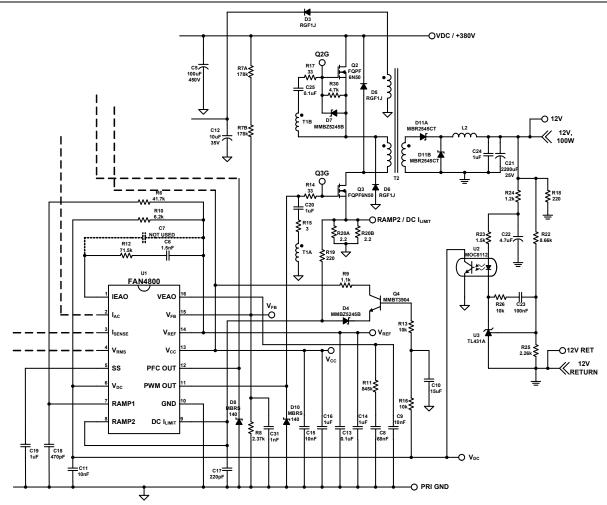

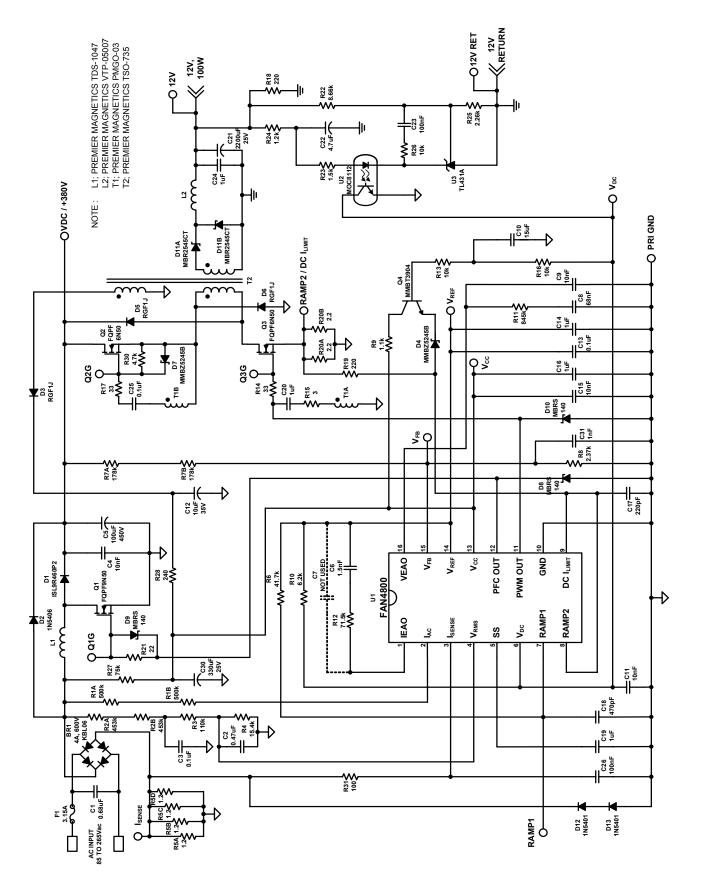

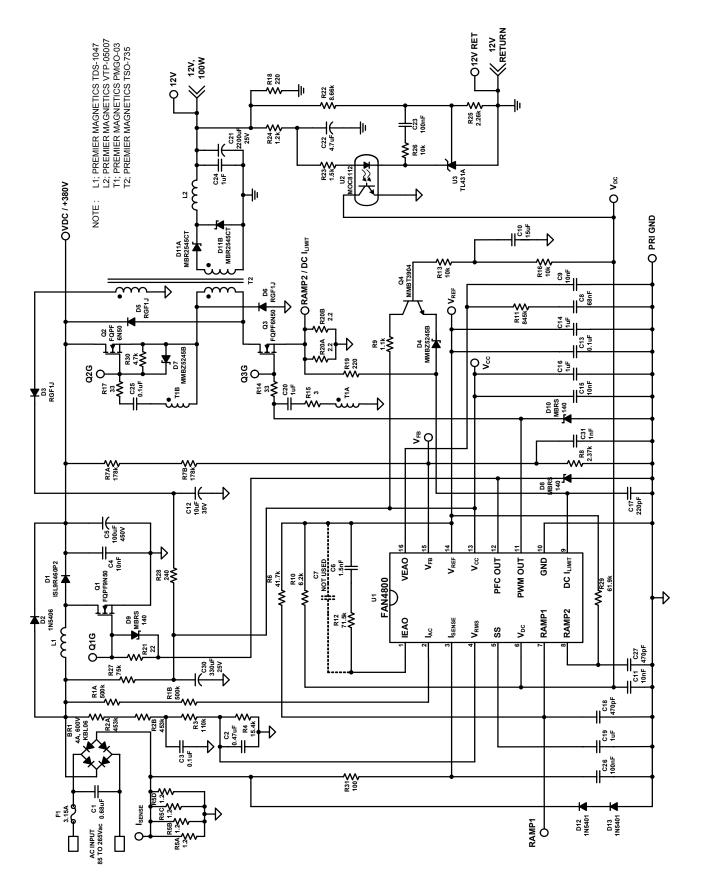

The complete power supply circuits shown in Figures 6 and 7 demonstrate the FAN4800's ability to manage high output power while complying with international requirements regarding AC line quality. The PFC section provides  $380V_{DC}$  to a dual-transistor current-mode forward converter. The output of the converter delivers +12V at up to 8.4 amps. The circuit operates from 85 to  $265V_{AC}$  with both power sections switching at 100kHz.

## The PFC Stage

#### Powering the FAN4800

The FAN4800 is initialized once  $C_{12}$  is charged to 13V through  $R_{27}$  and  $R_{28}$ . PFC switching action boosts the voltage on  $C_5$  to 380V via  $L_1$ 's inductance.  $T_2$  then supplies a well-regulated 13V for the FAN4800 from its secondary winding.  $T_2$ 's primary-to-secondary turns ratio ( $N_{PRI}$  /  $N_{SEC}$ ) is 18.8:1. For proper circuit operation, high-frequency bypassing with low-ESR ceramic or film capacitors on  $V_{CC}$  and  $V_{REF}$  is provided. Orderly PFC operation upon start-up is achieved when  $D_2$  quick charges the boost capacitor to the peak AC line voltage before the boost switch  $Q_1$  is turned on. This ensures the boost inductor current is zero before

PFC action begins. The value of the regulated voltage on  $C_5$  must always be greater than the peak value of the maximum line voltage delivered to the supply.

$$V_{CS} > \sqrt{2}V_{in(rms\_max)} \\ V_{CS} > (1.414) \times (265) \\ V_{CS} > 375V \quad use \ 380V$$

(1)

Because the FAN4800 uses transconductance amplifiers, the loop compensation networks are returned to ground (see the FAN4800 datasheet for the error amplifier characteristics/ advantages). This eliminates the interaction of the resistive divider network with the loop compensation capacitors, permitting a wide choice of divider values chosen to minimize amplifier offset voltages due to input bias currents. For reliable operation,  $R_{7A}$  and  $R_{7B}$  must have a voltage rating of at least 400 volts.

Calculate the divider ratio  $(R_{7A}+R_{7B})/R_8$  by:

$$\frac{\frac{R_{7A} + R_{7B}}{R_8}}{\frac{R_{7A} + R_{7B}}{R_8}} = \frac{V_{C5}}{2.5} - 1$$

$$\frac{R_{7A} + R_{7B}}{R_8} = \frac{380}{2.5} - 1$$

$$\frac{R_{7A} + R_{7B}}{R_8} = 151$$

(2)

#### Selecting the Power Components

The FAN4800 PFC section operates with continuous inductor current to minimize peak current and to maximize available power. The boost inductor value found by setting  $\Delta I$ , the peak-to-peak value of high-frequency current, is typically 10% to 20% of the peak value of the maximum line current.

$$I_{in(peak\_max)} = \frac{\sqrt{2}P_{in(max)}}{V_{in(rms\_min)}}$$

(3)

$$P_{in(max)} = \frac{P_{O(max)}}{\eta} \tag{4}$$

where  $I_{in(peak\_max)}$  is a peak value of input current occurred at low line,  $V_{in(rms\_min)}$  is RMS value of minimum line voltage,  $P_{O(max)}$  is the maximum output power, and  $\eta$  is efficiency. Value  $I_{in(peak\_max)}$  defines value of  $\Delta I$ , where dI is the specified percentage rate.  $I_{L(max)}$  is the inductor maximum current.

$$\Delta I = dI \times I_{in(peak_max)}$$

$$I_{L(max)} = I_{in(peak_max)} + \frac{\Delta I}{2}$$

(5)

Duty cycle D and switching frequency  $f_{\rm S}$  influence inductor selection.

$$D = \frac{V_O - \sqrt{2}V_{in(rms\_min)}}{V_O} \tag{6}$$

$$L_{I} = \frac{D \times \sqrt{2} V_{in(rms\_min)}}{f_{s} \times \Delta I} \tag{7}$$

$$= \frac{\left(V_{O} - \sqrt{2}V_{in(rms\_min)}\right) \cdot V_{in(rms\_min)}^{2} \cdot \eta}{V_{O} \cdot f_{S} \cdot dI \cdot P_{O(max)}}$$

=

$$\frac{\left\{380 - (1.414) \cdot (85)\right\} \cdot (85)^{2} \cdot (0.95)}{(380) \cdot (1 \times 10^{5}) \cdot (0.15) \cdot (100)}$$

=

$$3.128mH \qquad \text{use } 3.0mH$$

The boost diode  $D_1$  and switch  $Q_1$  are chosen with a reverse voltage rating of 500V to safely withstand the 380V boost potential. The maximum  $Q_1$  RMS current is obtained by Equation 8 and the maximum  $Q_1$  peak current is calculated by Equation 9.

$$I_{Q1rms} = \sqrt{2}I_{in(rms\_max)} \sqrt{\frac{1}{2} - \frac{4\sqrt{2}V_{in(rms\_min)}}{3\pi V_O}}$$

=  $\frac{\sqrt{2}P_{O(max)}}{\eta V_{in(rms\_min)}} \sqrt{\frac{1}{2} - \frac{4\sqrt{2}V_{in(rms\_min)}}{3\pi V_O}}$

=  $\frac{(1.414) \cdot (100)}{(0.95) \cdot (85)} \sqrt{\frac{1}{2} - \frac{4 \cdot (1.414) \cdot (85)}{3 \cdot (3.1416) \cdot (380)}}$

=  $1.06A$  (8)

$$I_{Q1peak} = I_{in(peak\_max)} + \frac{\Delta I}{2}$$

$$= \frac{\sqrt{2}P_{O(max)}}{\eta V_{in(rms\_min)}} + \frac{\left(V_O - \sqrt{2}V_{in(rms\_min)}\right) \cdot \sqrt{2}V_{in(rms\_min)}}{V_O \cdot f_S \cdot L_I} \qquad (9)$$

$$= \frac{(1.414) \cdot (100)}{(0.95) \cdot (85)} + \frac{\left(380 - (1.414) \cdot (85)\right) \cdot (1.414) \cdot (85)}{(380) \cdot (1 \times 10^5) \cdot (3 \times 10^{-3})}$$

$$= 2.025A$$

The boost diode average current can be calculated by:

$$I_{Dlavg} = I_{O(max)}$$

$$= \frac{P_{O(max)}}{V_O}$$

$$= \frac{100}{380} = 0.26 A$$

(10)

The boost capacitor value is chosen to permit a given output voltage hold-up time in the event the line voltage is suddenly removed.

$$C_{s} \ge \frac{2P_{O(max)}t_{HLD}}{V_{CS(NOM)^{2}} - V_{CS(MIN)}^{2}}$$

(11)

where:

$t_{HLD} =$  hold-up time (sec)

$$V_{C5(min)}$$

= minimum voltage on C<sub>5</sub> at which the PWM stage

can still deliver full output power

A key advantage of using leading/trailing-edge modulation is that a large portion of the inductor current is "dumped" directly into the load (PWM stage transformer) and not the boost capacitor. This relaxes the ESR requirement of the boost capacitor. For reference, Equation 12 should be used as a starting point when choosing  $C_5$ 's maximum ripple current rating (at 120Hz).

$$I_{CS\_rms} = \frac{I_{O(CS)}}{\sqrt{2}} \tag{12}$$

$$\left(I_{peak} = \sqrt{2} \cdot I_{C5\_rms}\right) \tag{12a}$$

#### Selecting the Power Setting Components

The maximum average power delivered by the PFC stage is set using the following procedure:

1. Find the resistive divider ratio that results in the voltage at the  $V_{RMS}$  pin being equal to 1.14V at the lowest line voltage. The voltage at this pin must be well filtered, yet able to respond well to transient line voltage changes.

$$\frac{R_4}{R_{TOT}} = \frac{1.14 \cdot \pi}{2\sqrt{2}V_{in(rms\_min)}}$$

(13)

The resistor and capacitor values in the typical example were found empirically to offer the lowest ripple voltage and still respond well to line voltage changes. Should a ratio be required that is greatly different from that found in Equation 13, adjust the filter capacitor values according to Equations 14 and 15.

$$C_{3} = \frac{R_{TOT}}{2\pi f_{I} \cdot (R_{2A} + R_{2B}) \cdot (R_{3} + R_{4})}$$

(14)

$$C_{2} = \frac{\left(1 + \frac{R_{4} \cdot R_{TOT}}{\left(R_{2A} + R_{2B}\right) \cdot \left(R_{3} + R_{4}\right)}\right)}{2\pi f_{2} \cdot R_{4}}$$

(15)

where:

AN6032

$$f_1 = 15Hz, f_2 = 23Hz$$

$R_{TOT} = R_{2A} + R_{2B} + R_3 + R_4$

2. Find the constant of proportionality  $k_M$  of the multiplier gain k in Equation 16a. To obtain "brownout" action below the lowest input voltage, the maximum gain of the multiplier must be used when finding  $k_M$ . The maximum gain (0.35) occurs when the  $V_{RMS}$  input of the multiplier is 1.14V. Equation 16 is the general expression for the multiplier gain versus the line voltage.

$$k = \frac{k_M}{V_{rms}^2} \tag{16}$$

$$k_M = kV_{in(rms\_min)}^2$$

(16a)

= (0.35) \cdot (85)^2

= 2528.75 \approx 2529

3. Select the value of  $(R_{1A}+R_{1B})$  that permits the greatest multiplier output current without saturating the output. The maximum output current of the multiplier is 228.57 $\mu$ A.

$$(R_{IA} + R_{IB}) \geq \frac{k\sqrt{2}V_{in(rms\_min)} (V_{EAO(max)} - 0.625)}{228.57 \times 10^{-6}} (R_{IA} + R_{IB}) \geq \frac{(0.35) \cdot (1.414) \cdot (85) (6 - 0.625)}{228.57 \times 10^{-6}}$$

(17)

$(R_{IA} + R_{IB}) \geq 989.38k\Omega$  use  $IM\Omega$

4. Select the value of the current sense resistor to complete the calculations for the power setting components.

$$R_{5A} || R_{5B} || R_{5C} || R_{5D} \le \frac{R_{MULO} \cdot k_M \left( V_{EAO(max)} - 0.625 \right) \cdot \eta}{P_{O(max)} \left( R_{IA} + R_{IB} \right)}$$

(18)

$$R_{5A} || R_{5B} || R_{5C} || R_{5D} \le \frac{\left( 3.5 \times 10^3 \right) \cdot \left( 2529 \right) \left( 6 - 0.625 \right) \cdot \left( 0.95 \right)}{\left( 100 \right) \left( 1 \times 10^6 \right)}$$

$$R_{5A} || R_{5B} || R_{5C} || R_{5D} \le 0.452\Omega \quad use \ 0.3\Omega$$

where:

$R_{MULO}$  = multiplier output termination resistance (3.5k $\Omega$ ).

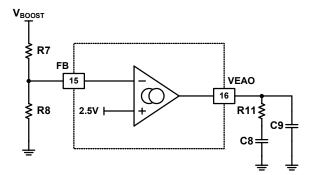

#### Voltage Loop Compensation

Maximum transient response of the PFC section, without instability, is obtained when the open-loop crossover frequency is one-half the line frequency. For this application, the compensation components (pole/zero pair) are chosen so that the closed loop response decreases at 20dB/decade, crossing unity gain at 30Hz, then immediately decreasing at 40dB/decade. The error amplifier pole is placed at 30Hz and an effective zero at one-tenth this frequency, or 3Hz. Find the crossover frequency ( $G_{PS} = 1$ ) of the power stage. For reference, Equation 20 finds the power stage pole and Equation 21 finds the power stage DC gain.

$$f_{c} = \frac{P_{in(max)}}{2\pi V_{O} \left( V_{EAO(max)} - 0.625 \right) C_{5}}$$

$$= \frac{P_{O(max)}}{2\pi \eta V_{O} \left( V_{EAO(max)} - 0.625 \right) C_{5}}$$

$$= \frac{100}{(2) \cdot (3.1416) \cdot (0.95) \cdot (380) \cdot (6 - 0.625) \cdot (100 \times 10^{-6})}$$

$$= 82.02 Hz$$

$$(19)$$

$$f_{P} = \frac{1}{\pi R_{L}C_{5}}$$

(20)

=  $\frac{1}{(3.1416) \cdot (1444) \cdot (100 \times 10^{-6})}$

= 2.20Hz

where:

$$R_L = \frac{V_O^2}{P_{O(max)}}$$

$$G_{PS(DC)} = \frac{\sqrt{2}f_C}{f_P}$$

(21)

=  $\frac{(1.414) \cdot (82.02)}{2.20}$

= 52.72 (34.44dB)

The gain of the power stage at 30Hz is calculated by:

$$G_{PS(30H_{c})} = \frac{f_{C}}{30}$$

(22)

=  $\frac{82.02}{30}$

= 2.734 (8.736dB)

The power stage gain is attenuated by the resistive divider  $(R_{7A}+R_{7B})/R_8$  according to Equation 23:

$$G_{RDIV} = \frac{R_8}{R_{7A} + R_{7B} + R_8}$$

(23)

=  $\frac{2.37}{178 + 178 + 2.37}$

=  $6.613 \times 10^{-3} (-43.59 dB)$

The amount of error amplifier gain required to bring the open-loop gain to unity at 30Hz is the negative of the sum of the power stage, plus divider stage gain (attenuation):

$$G_{EA} = -(G_{PS(30Hz)} + G_{RDIV})$$

(24)

= -(8.736 + (-43.59))

= 34.854dB (55.29V / V)

The value of  $R_{11}$ , which sets the high-frequency gain of the error amplifier, can be determined by:

$$R_{II} = \frac{G_{EA}}{g_M}$$

$$= \frac{55.29}{70 \times 10^{-6}}$$

$$= 789.8k\Omega \qquad use 845k\Omega$$

(25)

Calculate  $C_8$ ; which, together with  $R_{11}$ , sets the zero frequency at 3Hz.

$$C_{8} = \frac{1}{2\pi R_{11} f_{Z}}$$

(26)

=  $\frac{1}{(2) \cdot (3.1416) \cdot (845 \times 10^{3}) \cdot (3)}$

=  $62.8nF$  use  $68nF$

Since the pole frequency is ten times the zero frequency, the pole capacitor  $C_9$  is one-tenth the value of  $C_8$ .

$$C_{g} = \frac{C_{g}}{10}$$

$$= \frac{68 \times 10^{-9}}{10}$$

$$= 6.8nF \qquad use \ 10nF$$

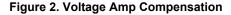

#### **Current Loop Compensation**

The current loop is compensated like the voltage loop, except the choice of the open-loop crossover frequency. To prevent interaction with the voltage loop, the current loop bandwidth should be greater than ten times the voltage loop crossover frequency, but no more than one sixth the switching frequency, or 16.7kHz. The power stage crossover frequency by Equation 28, the pole frequency by Equation 29, and the power stage DC gain by Equation 30.

Figure 3. Current Amp Compensation

$$f_{C} = \frac{(R_{5A} || R_{5B} || R_{5C} || R_{5D}) V_{O}}{2\pi L_{I} V_{RAMP_{IP-P}}}$$

$$= \frac{(0.3)(380)}{(2) \cdot (3.1416) \cdot (3 \times 10^{-3}) \cdot (2.75)}$$

$$= 2.2kHz$$

(28)

$$f_{P} = \frac{1}{\pi R_{L}C_{s}}$$

(29)

=  $\frac{1}{(3.1416) \cdot (1444) \cdot (100 \times 10^{-6})}$

= 2.20Hz same as (20)

$$G_{PS(DC)} = \frac{\sqrt{2}f_{C}}{f_{P}}$$

(30)

=  $\frac{(1.414) \cdot (2.20 \times 10^{3})}{2.20}$

= 1414 (63.0dB)

Find the gain of the power stage at 16.7kHz.

$$G_{PS(16.7kHz)} = \frac{f_C}{16.7 \times 10^3}$$

$$= \frac{2.20 \times 10^3}{16.7 \times 10^3}$$

$$= 1.32 \times 10^{-1} \ (-17.60dB)$$

(31)

The current loop contains no attenuating resistors, so find the error amplifier gain with:

$$G_{EA} = -(-G_{PS(16.7kHz)})$$

(32)

= -(-17.60)

= 17.60dB (7.58V/V)

Determine the value of the current error amplifier setting resistor  $R_{12}$ .

$$R_{12} = \frac{G_{EA}}{g_{M(CE)}}$$

(33)

=  $\frac{7.58}{85 \times 10^{-6}}$

=  $89.2k\Omega$  use 71.5k $\Omega$

Calculate the value of  $C_6$  to form the zero at 1.67kHz.

$$C_{6} = \frac{1}{2\pi R_{12} f_{Z}}$$

$$= \frac{1}{(2) \cdot (3.1416) \cdot (71.5 \times 10^{3}) \cdot (1.67 \times 10^{3})}$$

$$= 1.33nF \qquad use \ 1.5nF$$

(34)

The pole capacitor  $C_7$  is one-tenth the value of  $C_6$ .

$$C_{7} = \frac{C_{6}}{10}$$

(35)

=  $\frac{1.5 \times 10^{-9}}{10}$

=  $150 \, pF$

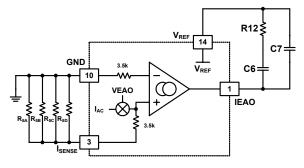

#### The PWM Stage

#### Soft-Starting the PWM Stage

The FAN4800 features a dedicated soft-start pin for controlling the rate of rise of the output voltage and preventing overshoot during power on. The controller does not initiate soft-start action until the PFC voltage reaches its nominal value, thereby preventing stalling of the output voltage due to excessive PFC currents. PWM action is terminated in the event the FAN4800 loses power or if the PFC boost voltage falls below  $228V_{DC}$ . The soft-start capacitor value (C<sub>19</sub>) for 50ms of delay is found by Equation 36.

$$C_{19} = (t_{SS}) \cdot \left(\frac{20 \times 10^{-6}}{0.95}\right)$$

(36)

=  $(0.05) \cdot \left(\frac{20 \times 10^{-6}}{0.95}\right)$

=  $1\mu F$

#### **Setting the Oscillator Frequency**

There is one version of the FAN4800. The FAN4800IN is where the PFC and PWM run at the same frequency.

#### **FAN4800IN**

In general, it is best to choose a small-valued capacitor  $C_{18}$  to maximize the oscillator duty cycle (minimize the  $C_{18}$  discharge time). Too small a value capacitor can increase the oscillator's sensitivity to phase modulation caused by stray field voltage induction into this node. For the practical

Figure 4. The PWM Stage

example, a 470pF capacitor is chosen for  $C_{18}$ . Equation 37 is accurate with values of  $R_6$  greater than 10k.

$$R_{6} \approx \frac{1}{0.51 \cdot f_{SW}C_{18}}$$

$$\approx \frac{1}{(0.51) \cdot (1 \times 10^{5}) \cdot (470 \times 10^{-12})}$$

$$\approx 41.7k\Omega$$

(37)

#### **Current Limit**

The PWM power stage operates in current mode using  $R_{20A}$  and  $R_{20B}$  to generate the voltage ramp for duty cycle control. The FAN4800 limits the maximum primary current via an internal 1V comparator; which, when exceeded, terminates the drive to the external power MOSFETs. Maximum primary current is:

$$I_{PRI(MAX)} = \frac{1}{R_{20A} || R_{20B}}$$

(38)

=  $\frac{2.2 + 2.2}{2.2 \times 2.2}$

= 0.91 Amps

#### Voltage Mode (Feedforward)

Should voltage mode control be used, it is necessary to know  $C_5$ 's peak voltage to choose the correct ramp generating components. Equation 39 finds the worst-case peak-to-peak ripple voltage across  $C_5$ . To find the peak voltage, divide the ripple voltage by two and add it to the regulated boost voltage. Remember that since the FAN4800 employs leading/ trailing modulation, the actual peak-to-peak ripple voltage is generally much less than the calculated value.

$$V_{R(CS)} = I_{OUT(CS)} \sqrt{\left(\frac{l}{4\pi f_L C_s}\right)^2 + ESR(C_s)^2}$$

(39)

where:

$f_L = line frequency.$

Solve Equation 40 for the ramp resistor value. The ramp capacitor value should be in the range of  $470 \text{pF} \sim 10 \text{nF}$ . Choose a resistor with an adequate voltage rating to withstand the boost voltage.

$$R_{RAMP} = \frac{\sigma_{(MAX)}}{C_{RAMP} f_{SW} ln \left( 1 - \frac{V_{REF}}{V_O + 0.5V_R} \right)}$$

(40)

where:

$\sigma_{(MAX)}$  = maximum PWM duty cycle (0.45 for the FAN4800)

$V_R$  = peak-to-peak boost capacitor ripple voltage for Equation 39.

#### The Power Transformer Turns Ratio

The minimum output voltage at the secondary of  $T_2$  is found in Equation 41. The secondary voltage is chosen to be 30 volts to increase the output voltage hold-up time.

$$V_{SEC(MIN)} = \frac{V_{OUT}}{\sigma_{(MAX)}} + V_F$$

$$= \frac{12}{0.45} + 1.0$$

$$= 27.7Volts$$

(41)

The transformer turns ratio is derived from Equation 42:

$$\frac{N_{PRI}}{N_{SEC}} = \frac{V_O}{V_{SEC(MN)}}$$

$$= \frac{380}{30}$$

$$N_{PRI} : N_{SEC} = 38 : 3$$

(42)

The maximum secondary current with the output shorted is limited by Equation 43:

$$I_{SEC(MAX)} = \frac{I_{PRI(MAX)}N_{PRI}}{N_{SEC}}$$

$$= \frac{(0.91) \cdot (38)}{3}$$

$$= 11.5 Amps$$

(43)

The output inductor and rectifier are chosen with maximum current rating larger than the maximum secondary current.

#### **Output Filter Component Filter Selection**

$L_2$ 's value is chosen to efficiently minimize output ripple current, thereby easing the ESR requirement of the filter capacitor.  $C_{21}$ 's ESR value is the dominant contributor to the output ripple. The maximum ESR value required is found in Equation 44:

$$ESR_{(C21)} \le \frac{V_R L_2 f_{SW}}{V_{SEC} \sigma_{(MAX)}}$$

(44)

where:

$V_R$  = peak-to-peak output ripple voltage.

© 2006 Fairchild Semiconductor Corporation

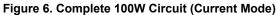

#### **Output Voltage Compensation**

A TL431 shunt regulator U<sub>3</sub> and opto-isolator U<sub>2</sub> perform output voltage setting and regulation. The opto crosses the primary-to-secondary safety boundary, varying the voltage on the V<sub>DC</sub> pin to keep the output voltage constant against line and load changes. Using current-mode control simplifies loop compensation, leaving only a single pole and zero in the output stage. The pole is created from the output capacitor and equivalent load resistance. The zero is formed from the filter capacitor and its ESR. In this example, the action of the zero occurs well after the closed-loop response has crossed unity, so it was not compensated with a pole. The output pole is canceled, increasing the overall bandwidth by the addition of  $R_{26}$  and  $C_{23}$ , which form a zero with TL431. For more information on using the TL431, including gain/phase versus frequency characteristics, refer to the Fairchild Semiconductor datasheet for the TL431.

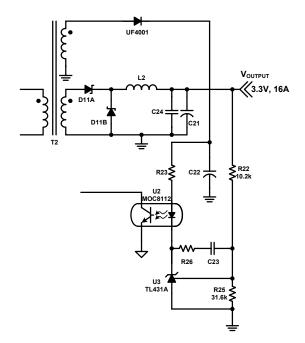

#### 3.3V Output Design Changes

The latest microprocessors and support circuitry require a 3.3V supply for proper operation. The FAN4800 is ideal for these applications, including the energy-efficient, ecologically friendly "Green" PC. If the total output power required varies greatly from 100 watts, it is necessary to re-select certain components, beginning with the PFC stage. T<sub>2</sub>'s turn ratio must be adjusted according to Equation 42 and another low-current secondary winding added using the same turns ratio as originally found for the +12 volts. This second winding is necessary to power the TL431/opto circuit because the 3.3V output is not adequate to fully bias the feedback circuitry. C<sub>21</sub> may be increased to reduce the output ripple voltage. Figure 5 displays a 3.3V output stage capable of supplying 16 amps.

Figure 5. 3.3V Output Stage

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1.Life support devices or systems are devices or systems which,

- (a) are intended for surgical implant into the body, or

- (b) support or sustain life, or

- (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- 2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor haves against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death a

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

© Semiconductor Components Industries, LLC