**Product brief**

## 1 General description

The MC33771C is a SMARTMOS lithium-ion battery cell controller IC designed for automotive applications, such as hybrid electric (HEV) and electric vehicles (EV) along with industrial applications, such as energy storage systems (ESS) and uninterruptible power supply (UPS) systems.

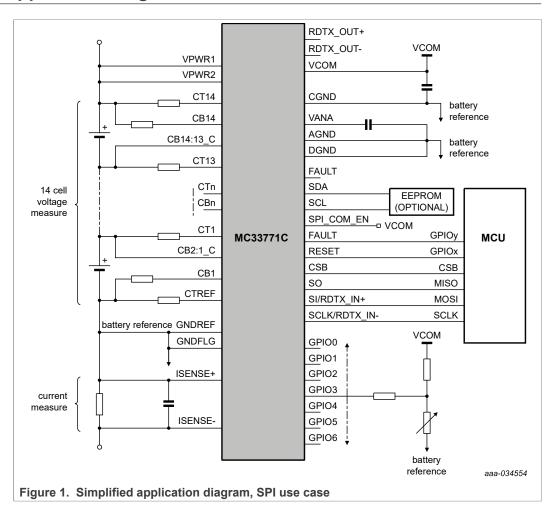

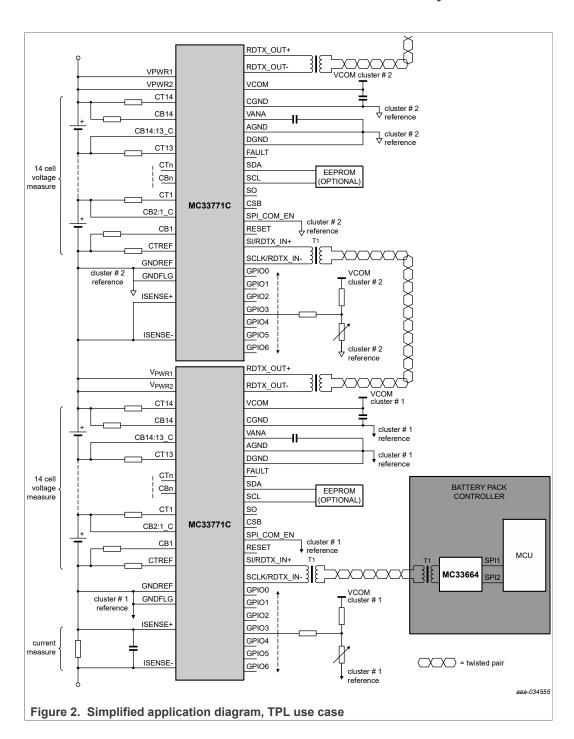

The device performs ADC conversions of the differential cell voltages and current, as well as battery coulomb counting and battery temperature measurements. The information is transmitted to MCU using one of the microcontroller interfaces (Serial Peripheral Interface (SPI) or Transformer physical layer (TPL)) of the IC.

#### 2 Features

- 9.6 V ≤ V<sub>PWR</sub> ≤ 63 V operation, 75 V transient

- 7 to 14 cells management

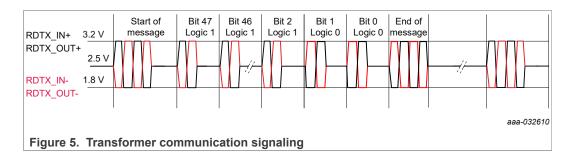

- Isolated 2.0 Mbps differential communication or 4.0 Mbps SPI

- · Addressable on initialization

- Bi-directional transceiver to support up to 63 nodes in daisy chain

- 0.8 mV maximum total voltage measurement error

- Synchronized cell voltage/current measurement with coulomb count

- · Averaging of cell voltage measurements

- · Total stack voltage measurement

- Seven GPIO/temperature sensor inputs

- 5.0 V at 5.0 mA reference supply output

- Automatic over/undervoltage and temperature detection routable to fault pin

- · Integrated sleep mode over/undervoltage and temperature monitoring

- · Onboard 300 mA passive cell balancing with diagnostics

- Hot plug capable

- Detection of internal and external faults, as open lines, shorts, and leakages

- Designed to support ISO 26262, up to ASIL D safety system.

- Qualified in compliance with AECQ-100

# 3 Simplified application diagram

# 4 Applications

- Automotive: 48 V and high-voltage battery packs

- · E-bikes, e-scooters

- · Energy storage systems

- Uninterruptible power supply (UPS)

# 5 Ordering information

## 5.1 Part numbers definition

# MC33771C T/<u>y</u> <u>z</u> AE/R2

Table 1. Part number breakdown

| Code | Option | Description                                     |

|------|--------|-------------------------------------------------|

|      | Т      | TPL communication type                          |

| V    | Р      | y = P (Premium with current measurement option) |

| y    | Α      | y = A (Advanced)                                |

| -    | 1      | z = 1 (7 to 14 channels)                        |

| Z    | 2      | z = 2 (7 to 8 channels)                         |

|      | AE     | Package suffix                                  |

|      | R2     | Tape and reel indicator                         |

#### 5.2 Part numbers list

This section describes the part numbers available to be purchased along with their differences. Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to <a href="http://www.nxp.com">http://www.nxp.com</a>.

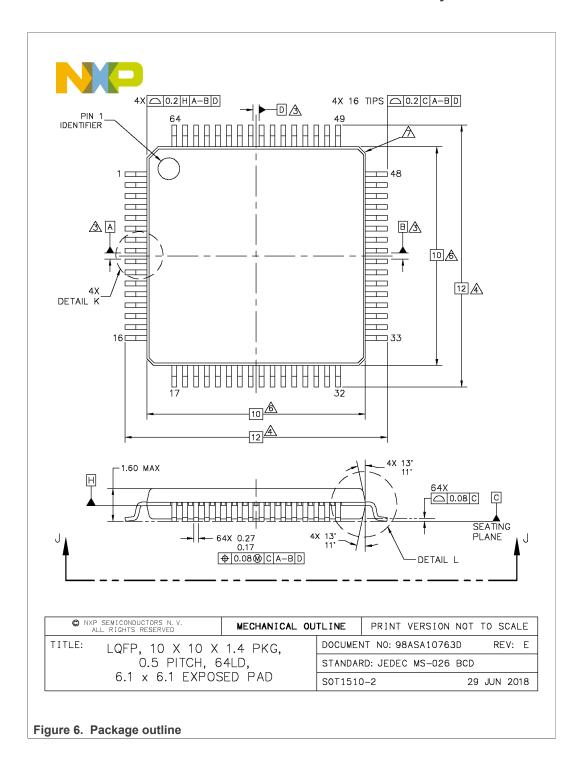

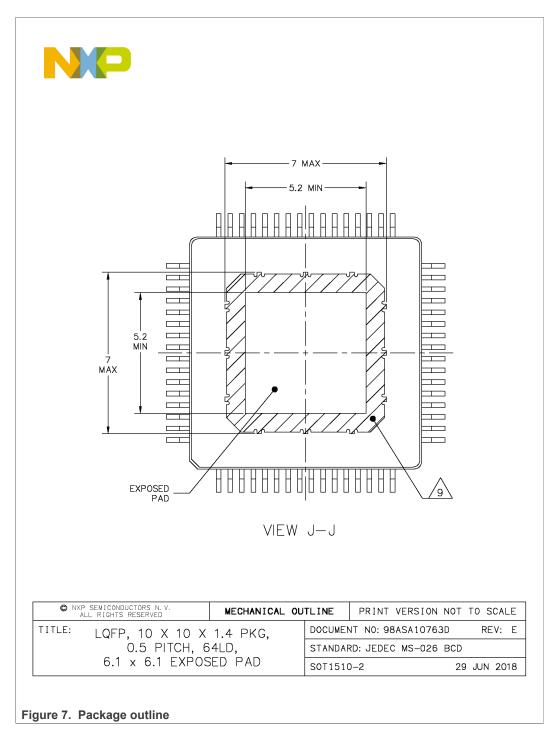

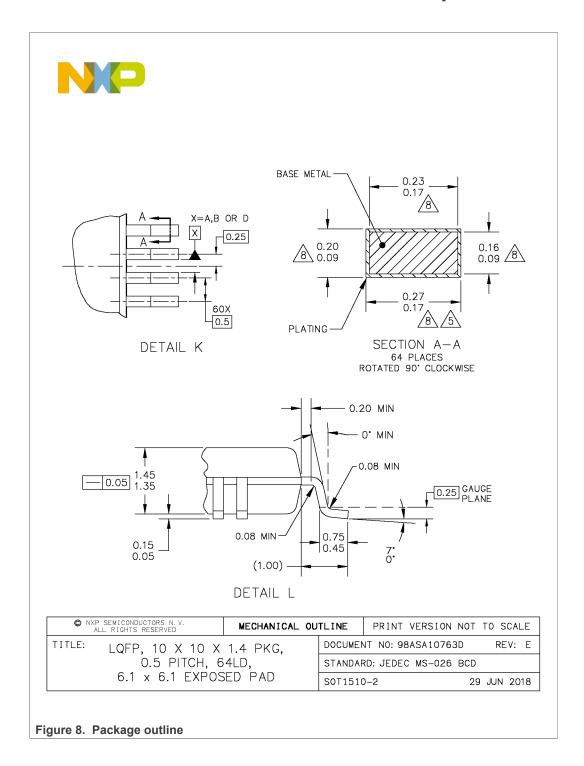

Table 2. Advanced orderable part table Temperature range is −40 to 105 °C

Package type is 64-pin LQFP-EP

| Orderable part Number of channels OV/UV Precision GPIO as temperature coulomb count Current channel of channels and OT/UT Coulomb count |        |     |     |    |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|----|--|--|--|

| TPL differential communication protocol                                                                                                 |        |     |     |    |  |  |  |

| MC33771CTA1AE 7 to 14 Yes Yes No                                                                                                        |        |     |     |    |  |  |  |

| MC33771CTA2AE                                                                                                                           | 7 to 8 | Yes | Yes | No |  |  |  |

Table 3. Premium orderable part table Temperature range is −40 to 105 °C Package type is 64-pin LQFP-EP

| Orderable part Number of channels OV/UV Precision GPIO as temperature channel of coulomb count |        |     |     |     |  |  |  |

|------------------------------------------------------------------------------------------------|--------|-----|-----|-----|--|--|--|

| TPL differential communication protocol with current measurement option                        |        |     |     |     |  |  |  |

| MC33771CTP1AE 7 to 14 Yes Yes Yes                                                              |        |     |     |     |  |  |  |

| MC33771CTP2AE                                                                                  | 7 to 8 | Yes | Yes | Yes |  |  |  |

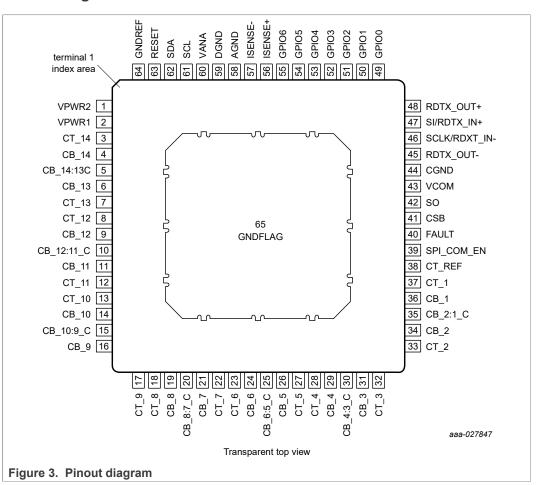

# 6 Pinning information

## 6.1 Pinout diagram

#### 6.2 Pin definitions

Table 4. Pin definitions

| Number | Name       | Function | Definition                                                                |

|--------|------------|----------|---------------------------------------------------------------------------|

| 1      | VPWR2      | Input    | Power input to the MC33771C                                               |

| 2      | VPWR1      | Input    | Power input to the MC33771C                                               |

| 3      | CT_14      | Input    | Cell pin 14 input. Terminate to LPF resistor.                             |

| 4      | CB_14      | Output   | Cell balance driver. Terminate to cell 14 cell balance load resistor.     |

| 5      | CB_14:13_C | Output   | Cell balance 14:13 common. Terminate to CB_14:13_C balance load resistor. |

| 6      | CB_13      | Output   | Cell balance driver. Terminate to cell 13 cell balance load resistor.     |

| 7      | CT_13      | Input    | Cell pin 13 input. Terminate to LPF resistor.                             |

| 8      | CT_12      | Input    | Cell pin 12 input. Terminate to LPF resistor.                             |

PB\_MC33771C

All information provided in this document is subject to legal disclaimers.

Table 4. Pin definitions...continued

| Number | Name       | Function | Definition                                                                |

|--------|------------|----------|---------------------------------------------------------------------------|

| 9      | CB_12      | Output   | Cell balance driver. Terminate to cell 12 cell balance load resistor.     |

| 10     | CB_12:11_C | Output   | Cell balance 12:11 common. Terminate to CB_12:11_C balance load resistor. |

| 11     | CB_11      | Output   | Cell balance driver. Terminate to cell 11 cell balance load resistor.     |

| 12     | CT_11      | Input    | Cell pin 11 input. Terminate to LPF resistor.                             |

| 13     | CT_10      | Input    | Cell pin 10 input. Terminate to LPF resistor.                             |

| 14     | CB_10      | Output   | Cell balance driver. Terminate to cell 10 cell balance load resistor.     |

| 15     | CB_10:9_C  | Output   | Cell balance 10:9 common. Terminate to CB_ 10:9_C balance load resistor.  |

| 16     | CB_9       | Output   | Cell balance driver. Terminate to cell 9 cell balance load resistor.      |

| 17     | CT_9       | Input    | Cell pin 9 input. Terminate to LPF resistor.                              |

| 18     | CT_8       | Input    | Cell pin 8 input. Terminate to LPF resistor.                              |

| 19     | CB_8       | Output   | Cell balance driver. Terminate to cell 8 cell balance load resistor.      |

| 20     | CB_8:7_C   | Output   | Cell balance 8:7 common. Terminate to CB_8:7_C balance load resistor.     |

| 21     | CB_7       | Output   | Cell balance driver. Terminate to cell 7 cell balance load resistor.      |

| 22     | CT_7       | Input    | Cell pin 7 input. Terminate to LPF resistor.                              |

| 23     | CT_6       | Input    | Cell pin 6 input. Terminate to LPF resistor.                              |

| 24     | CB_6       | Output   | Cell balance driver. Terminate to cell 6 cell balance load resistor.      |

| 25     | CB_6:5_C   | Output   | Cell balance 6:5 common. Terminate to CB_6:5_C balance load resistor.     |

| 26     | CB_5       | Output   | Cell balance driver. Terminate to cell 5 cell balance load resistor.      |

| 27     | CT_5       | Input    | Cell pin 5 input. Terminate to LPF resistor.                              |

| 28     | CT_4       | Input    | Cell pin 4 input. Terminate to LPF resistor.                              |

| 29     | CB_4       | Output   | Cell balance driver. Terminate to cell 4 cell balance load resistor.      |

| 30     | CB_4:3_C   | Output   | Cell balance 4:3 common. Terminate to CB_4:3_C balance load resistor.     |

| 31     | CB_3       | Output   | Cell balance driver. Terminate to cell 3 cell balance load resistor.      |

| 32     | CT_3       | Input    | Cell pin 3 input. Terminate to LPF resistor.                              |

| 33     | CT_2       | Input    | Cell pin 2 input. Terminate to LPF resistor.                              |

| 34     | CB_2       | Output   | Cell balance driver. Terminate to cell 2 cell balance load resistor.      |

Table 4. Pin definitions...continued

| Number | Name          | Function | Definition                                                                                             |

|--------|---------------|----------|--------------------------------------------------------------------------------------------------------|

| 35     | CB_2:1_C      | Output   | Cell Balance 2:1 common. Terminate to CB_2:1_C balance load resistor.                                  |

| 36     | CB_1          | Output   | Cell balance driver. Terminate to cell 1 cell balance load resistor.                                   |

| 37     | CT_1          | Input    | Cell pin 1 input. Terminate to LPF resistor.                                                           |

| 38     | CT_REF        | Input    | Cell pin REF input. Terminate to LPF resistor.                                                         |

| 39     | SPI_COM_EN    | Input    | SPI communication enable. Pin must be high for the SPI to be active.                                   |

| 40     | FAULT         | Output   | Fault output dependent on user defined internal or external faults. If not used, it must be left open. |

| 41     | CSB           | Input    | SPI chip select                                                                                        |

| 42     | so            | Output   | SPI serial output                                                                                      |

| 43     | VCOM          | Output   | Communication regulator output                                                                         |

| 44     | CGND          | Ground   | Communication decoupling ground. Terminate to GNDREF.                                                  |

| 45     | RDTX_OUT-     | I/O      | Receive/transmit output negative                                                                       |

| 46     | SCLK/RDTX_IN- | I/O      | SPI clock or receive/transmit input negative                                                           |

| 47     | SI/RDTX_IN+   | I/O      | SPI serial input or receive/transmit input positive                                                    |

| 48     | RDTX_OUT+     | I/O      | Receive/transmit output positive                                                                       |

| 49     | GPIO0         | I/O      | General purpose analog input or GPIO or wake-up or fault daisy chain                                   |

| 50     | GPIO1         | I/O      | General purpose analog input or GPIO                                                                   |

| 51     | GPIO2         | I/O      | General purpose analog input or GPIO or conversion trigger                                             |

| 52     | GPIO3         | I/O      | General purpose analog input or GPIO                                                                   |

| 53     | GPIO4         | I/O      | General purpose analog input or GPIO                                                                   |

| 54     | GPIO5         | I/O      | General purpose analog input or GPIO                                                                   |

| 55     | GPIO6         | I/O      | General purpose analog input or GPIO                                                                   |

| 56     | ISENSE+       | Input    | Current measurement input+                                                                             |

| 57     | ISENSE-       | Input    | Current measurement input-                                                                             |

| 58     | AGND          | Ground   | Analog ground, terminate to GNDREF                                                                     |

| 59     | DGND          | Ground   | Digital ground, terminate to GNDREF                                                                    |

| 60     | VANA          | Output   | Precision ADC analog supply                                                                            |

| 61     | SCL           | I/O      | I <sup>2</sup> C clock                                                                                 |

| 62     | SDA           | I/O      | I <sup>2</sup> C data                                                                                  |

| 63     | RESET         | Input    | RESET is an active high input. RESET has an internal pull down. If not used, it can be tied to GND.    |

Table 4. Pin definitions...continued

| Number | Name    | Function | Definition                                                              |

|--------|---------|----------|-------------------------------------------------------------------------|

| 64     | GNDREF  | Ground   | Ground reference for device. Terminate to reference of battery cluster. |

| 65     | GNDFLAG | Ground   | Device flag. Terminate to lowest potential of battery cluster.          |

# 7 General product characteristics

## 7.1 Ratings and operating requirements relationship

The operating voltage range pertains to the VPWR pins referenced to the AGND pins.

Table 5. Ratings vs. operating requirements

| Fatal range                         | На                                                                                           | Handling range – no permanent failure     |                                                                                                                                           |                                     |  |  |  |

|-------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|--|

| Permanent<br>failure might<br>occur | Lower limited operating range  No permanent failure, but IC functionality is not guaranteed  | Normal operating range • 100 % functional | Upper limited operating range     IC parameters might be out of specification     Detection of V <sub>PWR</sub> overvoltage is functional | Permanent<br>failure might<br>occur |  |  |  |

| V <sub>PWR</sub> < -0.3 V           | 7.6 V ≤ V <sub>PWR</sub> < 9.6 V<br><b>Reset range:</b><br>-0.3 V ≤ V <sub>PWR</sub> < 7.6 V | 9.6 V ≤ V <sub>PWR</sub> ≤ 63 V           | 63 V < V <sub>PWR</sub> ≤ 75 V                                                                                                            | 75 V < V <sub>PWR</sub>             |  |  |  |

In both upper and lower limited operating range, no information can be provided about IC performance. Only the detection of  $V_{PWR}$  overvoltage is guaranteed in the upper limited operating range.

Performance in normal operating range is guaranteed only if there is a minimum of seven battery cells in the stack.

## 7.2 Maximum ratings

Table 6. Maximum ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                                                                              | Description (rating)                                    | Min  | Max       | Unit |

|-------------------------------------------------------------------------------------|---------------------------------------------------------|------|-----------|------|

| Electrical ratings                                                                  |                                                         |      | '         |      |

| VPWR1, VPWR2                                                                        | Supply input voltage                                    | -0.3 | 75        | V    |

| CT14                                                                                | Cell terminal voltage                                   | -0.3 | 75        | V    |

| VPWR to CT14                                                                        | Voltage across VPWR1,2 pins pair and CT14 pin           | -10  | 10.5      | V    |

| CT <sub>N</sub> to CT <sub>N-1</sub>                                                | Cell terminal differential voltage [1]                  | -0.3 | 6.0       | V    |

| CT <sub>REF</sub> to GND                                                            | Cell terminal reference to ground                       | _    | 5         | V    |

| CT <sub>N</sub> to GND                                                              | Cell terminal voltage to ground (N=1 to 4 or N=6 to 14) | _    | (N+1) * 5 | V    |

|                                                                                     | Cell terminal voltage to ground (N=5)                   | _    | 27.5      | V    |

| CT <sub>N(CURRENT)</sub>                                                            | Cell terminal input current                             | _    | ±500      | μΑ   |

| CB <sub>N</sub> to CB <sub>N:N-1_C</sub> CB <sub>N:N-1_C</sub> to CB <sub>N-1</sub> | Cell balance differential voltage                       | _    | 10        | V    |

PB\_MC33771C

All information provided in this document is subject to legal disclaimers.

Table 6. Maximum ratings...continued

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                         | Description (rating)                                                                                                                                                                                                                                                                                                                        | Min   | Max                                  | Unit |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------|------|

| CB <sub>2n</sub> to GND        | Cell balance voltage to GND (n=1 to 7)                                                                                                                                                                                                                                                                                                      | _     | (2n+1) . 5                           | V    |

| CB <sub>2n+1</sub> to GND      | Cell balance voltage to GND (n=0 to 6)                                                                                                                                                                                                                                                                                                      | _     | (2n+1) . 5                           | V    |

| CB <sub>2n:2n-1_C</sub> to GND | Cell balance voltage to GND (n=1 to 6)                                                                                                                                                                                                                                                                                                      | _     | 2n . 5                               | V    |

| CB <sub>N:N-1_C</sub> to CTn-1 | Cell balance input to cell terminal input                                                                                                                                                                                                                                                                                                   | -10   | 10                                   | V    |

| VISENSE                        | ISENSE+ and ISENSE– pin voltage                                                                                                                                                                                                                                                                                                             | -0.3  | 2.5                                  | V    |

| VCOM                           | Maximum voltage may be applied to VCOM pin from external source                                                                                                                                                                                                                                                                             | _     | 5.8                                  | V    |

| VANA                           | Maximum voltage may be applied to VANA pin                                                                                                                                                                                                                                                                                                  | _     | 3.1                                  | V    |

| $V_{GPIO0}$                    | GPIO0 pin voltage                                                                                                                                                                                                                                                                                                                           | -0.3  | 6.5                                  | V    |

| V <sub>GPIOx</sub>             | GPIOx pins (x = 1 to 6) voltage                                                                                                                                                                                                                                                                                                             | -0.3  | VCOM +<br>0.5                        | V    |

| $V_{DIG}$                      | Voltage I <sup>2</sup> C pins (SDA, SCL)                                                                                                                                                                                                                                                                                                    | -0.3  | VCOM +<br>0.5                        | V    |

| V <sub>RESET</sub>             | RESET pin                                                                                                                                                                                                                                                                                                                                   | -0.3  | 6.5                                  | V    |

| V <sub>CSB</sub>               | CSB pin                                                                                                                                                                                                                                                                                                                                     | -0.3  | 6.5                                  | V    |

| V <sub>SPI_COMM_EN</sub>       | SPI_COMM_EN                                                                                                                                                                                                                                                                                                                                 | -0.3  | 6.5                                  | V    |

| V <sub>SO</sub>                | SO pin                                                                                                                                                                                                                                                                                                                                      | -0.3  | VCOM +<br>0.5                        | V    |

| V <sub>GPIO5,6</sub>           | Maximum voltage for GPIO5 and GPIO6 pins used as current input                                                                                                                                                                                                                                                                              | -0.3  | 2.5                                  | V    |

| FAULT                          | Maximum applied voltage to pin                                                                                                                                                                                                                                                                                                              | -0.3  | 7.0                                  | V    |

| I <sub>pin_unpowered</sub>     | Input current in a pin when the device is unpowered                                                                                                                                                                                                                                                                                         | -2    | 2                                    | mA   |

| V <sub>COMM</sub>              | Maximum voltage to pins RDTX_OUT+, RDTX_OUT-, SI/RDTX_IN+, SCLK/RDTX_IN-                                                                                                                                                                                                                                                                    | -10.0 | 10.0                                 | V    |

| V <sub>ESD1</sub>              | ESD voltage Human body model (HBM) Charge device model (CDM) Charge device model corner pins (CDM)                                                                                                                                                                                                                                          |       | ±2000<br>±500 <sup>[2]</sup><br>±750 | V    |

| $V_{ESD2}$                     | ESD voltage (VPWR1, VPWR2, CTx, CBx, GPIOx, ISENSE+, ISENSE-, RDTX_OUT+, RDTX_OUT-, SI/RDTX_IN+, SCLK/ RDTX_IN-) versus all ground pins  Human body model (HBM)                                                                                                                                                                             | _     | ±4000                                | V    |

| V <sub>ESD3</sub>              | ESD voltage (CTREF, CTx, CBx, GPIOx, ISENSE+, ISENSE-, RDTX_OUT+, RDTX_OUT-, SI/RDTX_IN+, SCLK/ RDTX_IN-) IEC 61000-4-2, Unpowered (Gun configuration: 330Ω / 150pF) HMM, Unpowered (Gun configuration: 330Ω / 150pF) ISO 10605:2009, Unpowered (Gun configuration: 2 kΩ / 150pF) ISO 10605:2009, Powered (Gun configuration: 2 kΩ / 150pF) |       | ±8000<br>±8000<br>±8000<br>±8000     | V    |

Adjacent CT pins may experience an overvoltage that exceeds their maximum rating during OV/UV functional verification test or during open line diagnostic test. Nevertheless, the IC is completely tolerant to this special situation. For CT\_REF pin applicable limit is ±450 V.

PB\_MC33771C

All information provided in this document is subject to legal disclaimers.

- [3] ESD testing is performed in accordance with the human body model (HBM) (C<sub>ZAP</sub> = 100 pF, R<sub>ZAP</sub> = 1500 Ω), and the charge device model (CDM) (C<sub>ZAP</sub> = 4.0 pF).

- [4] These voltage values can be sustained only if ESD caps are used as described in MC33771C External Components

#### 7.3 Thermal characteristics

#### Table 7. Thermal ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                 | Description (rating)                                                        |            | Min | Max  | Unit |

|------------------------|-----------------------------------------------------------------------------|------------|-----|------|------|

| Thermal rating         | gs                                                                          |            | ,   |      | ·    |

|                        | Operating temperature                                                       |            |     |      | °C   |

| $T_A$                  | Ambient                                                                     |            | -40 | +105 |      |

| $T_J$                  | Junction <sup>[1]</sup>                                                     |            | -40 | +150 |      |

| T <sub>STG</sub>       | Storage temperature                                                         |            | -55 | +150 | °C   |

| T <sub>PPRT</sub>      | Peak package reflow temperature                                             | [2]<br>[3] | _   | 260  | °C   |

| Thermal resis          | tance and package dissipation ratings                                       |            |     | '    | ,    |

| $R_{\Theta JB}$        | Junction-to-board (bottom exposed pad soldered to board) 64 LQFP EP         | [4]        | _   | 10   | °C/W |

| $R_{\Theta JA}$        | Junction-to-ambient, natural convection, single-layer board (1s) 64 LQFP EP | [5]<br>[6] | _   | 59   | °C/W |

| $R_{\Theta JA}$        | Junction-to-ambient, natural convection, four-layer board (2s2p) 64 LQFP EP | [5]<br>[6] | _   | 27   | °C/W |

| R <sub>OJCTOP</sub>    | Junction-to-case top (exposed pad) 64 LQFP EP                               | [7]        | _   | 14   | °C/W |

| R <sub>OJCBOTTOM</sub> | Junction-to-case bottom (exposed pad) 64 LQFP EP                            | [8]        | _   | 0.97 | °C/W |

| $\Psi_{JT}$            | Junction to package top, natural convection                                 | [9]        | _   | 3    | °C/W |

- [1] The user must ensure that the average maximum operating junction temperature (TJ) is not exceeded.

- [2] Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause a malfunction or permanent damage to the device.

- [3] NXP's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), go to <a href="https://www.nxp.com">www.nxp.com</a>, search by part number (remove prefixes/suffixes) and enter the core ID to view all orderable parts and review parametrics.

- [4] Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- [5] Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- [6] Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

- Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1), with the cold plate temperature used for the case temperature.

- [8] Thermal resistance between the die and the solder pad on the bottom of the package based on simulation without any interface resistance.

- Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2.

#### 7.4 Electrical characteristics

#### Table 8. Static and dynamic electrical characteristics

Characteristics noted under conditions 9.6 V  $\leq$  V<sub>PWR</sub>  $\leq$  63 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C, GND = 0 V, unless otherwise stated. Typical values refer to V<sub>PWR</sub> = 56 V, T<sub>A</sub> = 25 °C, unless otherwise noted.

| Symbol               | Parameter                    | Min | Тур | Max | Unit |  |  |

|----------------------|------------------------------|-----|-----|-----|------|--|--|

| Power management     |                              |     |     |     |      |  |  |

| V <sub>PWR(FO)</sub> | Supply voltage               |     |     |     | ٧    |  |  |

|                      | Full parameter specification | 9.6 | _   | 63  |      |  |  |

PB\_MC33771C All information provided in this document is subject to legal disclaimers.

Table 8. Static and dynamic electrical characteristics...continued

Characteristics noted under conditions 9.6 V  $\leq$  V<sub>PWR</sub>  $\leq$  63 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C, GND = 0 V, unless otherwise stated. Typical values refer to V<sub>PWR</sub> = 56 V, T<sub>A</sub> = 25 °C, unless otherwise noted.

| Symbol                      | Parameter                                                                                                                                                                             | Min | Тур  | Max      | Unit |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|----------|------|

| lvpwr                       | Supply current (base value)  Normal mode, cell balance OFF, ADC inactive, SPI communication inactive, IVCOM = 0 mA                                                                    | _   | 5.4  | _        | mA   |

|                             | Normal mode, cell balance OFF, ADC inactive, TPL communication inactive, IVCOM = 0 mA                                                                                                 | _   | 8.0  | _        |      |

| VPWR(TPL_TX)                | Supply current adder when TPL communication active                                                                                                                                    | _   | _    | 16       | mA   |

| VPWR(CBON)                  | Supply current adder to set all 14 cell balance switches ON                                                                                                                           | _   | 0.97 | _        | mA   |

| VPWR(ADC)                   | Delta supply current to perform ADC conversions (addend) ADC1-A,B continuously converting                                                                                             | _   | 3.0  | _        | mA   |

| lvpwr(ss)                   | ADC2 continuously converting  Supply current in sleep mode and in idle mode, communication inactive, cell balance off, cyclic measurement off, oscillator monitor on SPI mode (25 °C) |     | 1.4  |          | μΑ   |

|                             | TPL mode (T <sub>A</sub> = 25 °C)                                                                                                                                                     | 64  | _    | 108      |      |

| I <sub>VPWR(CKMON)</sub>    | Clock monitor current consumption                                                                                                                                                     | _   | 5    | _        | μA   |

| V <sub>PWR(OV_FLAG)</sub>   | V <sub>PWR</sub> overvoltage fault threshold (flag)                                                                                                                                   | _   | 65   | _        | V    |

| V <sub>PWR(LV_FLAG)</sub>   | V <sub>PWR</sub> low-voltage warning threshold (flag)                                                                                                                                 | _   | 12   | _        | V    |

| V <sub>PWR(UV_POR)</sub>    | V <sub>PWR</sub> undervoltage shutdown threshold (POR)                                                                                                                                | _   | 8.5  | _        | V    |

| V <sub>PWR(HYS)</sub>       | V <sub>PWR</sub> UV hysteresis voltage                                                                                                                                                | _   | 200  | _        | mV   |

| tvpwr(filter)               | V <sub>PWR</sub> OV, LV filter                                                                                                                                                        | _   | 50   | _        | μs   |

| VCOM power supp             | oly                                                                                                                                                                                   |     | '    | '        |      |

| V <sub>COM</sub>            | VCOM output voltage                                                                                                                                                                   | _   | 5.0  | _        | V    |

| lvсом                       | VCOM output current allocated for external use                                                                                                                                        | _   | _    | 5.0      | mA   |

| V <sub>COM(UV)</sub>        | VCOM undervoltage fault threshold                                                                                                                                                     | _   | 4.4  | _        | ٧    |

| V <sub>COM_HYS</sub>        | VCOM undervoltage hysteresis                                                                                                                                                          | _   | 100  | _        | mV   |

| VCOM(FLT_TIMER)             | VCOM undervoltage fault timer                                                                                                                                                         | _   | 10   |          | μs   |

| VCOM(RETRY)                 | VCOM fault retry timer                                                                                                                                                                | _   | 10   | _        | ms   |

| $V_{COM(OV)}$               | VCOM overvoltage fault threshold                                                                                                                                                      | 5.4 | _    | 5.9      | V    |

| I <sub>LIM_</sub> VCOM(OC)  | VCOM current limit                                                                                                                                                                    | 65  | _    | 140      | mA   |

| R <sub>VCOM(SS)</sub>       | VCOM sleep mode pull-down resistor                                                                                                                                                    | _   | 2.0  | _        | kΩ   |

| tvсом                       | VCOM rise time (for $V_{PWR}$ > 10V and CL = 2.2 $\mu F$ (ceramic X7R only) in parallel with 220 pF)                                                                                  | _   | _    | 440      | μs   |

| VANA power supp             | ly                                                                                                                                                                                    |     |      |          |      |

| V <sub>ANA</sub>            | VANA output voltage (not used by external circuits) Decouple with 47 nF X7R 0603 or 0402                                                                                              | _   | 2.65 | _        | V    |

| V <sub>ANA(UV)</sub>        | VANA undervoltage fault threshold                                                                                                                                                     | _   | 2.4  | _        | V    |

| V <sub>ANA_HYS</sub>        | VANA undervoltage hysteresis                                                                                                                                                          | _   | 50   | _        | mV   |

| V <sub>ANA(FLT_TIMER)</sub> | VANA undervoltage fault timer                                                                                                                                                         | _   | 11   | _        | μs   |

| V <sub>ANA(OV)</sub>        | VANA overvoltage fault threshold                                                                                                                                                      | _   | 2.8  | _        | V    |

| t <sub>VANA(RETRY)</sub>    | VANA fault retry timer                                                                                                                                                                | _   | 10   | <u> </u> | ms   |

PB\_MC33771C

All information provided in this document is subject to legal disclaimers.

Table 8. Static and dynamic electrical characteristics...continued

Characteristics noted under conditions 9.6 V  $\leq$  V<sub>PWR</sub>  $\leq$  63 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C, GND = 0 V, unless otherwise stated. Typical values refer to V<sub>PWR</sub> = 56 V, T<sub>A</sub> = 25 °C, unless otherwise noted.

| Symbol                     | Parameter                                                                                                                                                                                                                       | Min  | Тур                 | Max      | Unit   |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|----------|--------|

| I <sub>LIM_VANA(OC)</sub>  | VANA current limit                                                                                                                                                                                                              | 5.0  | _                   | 10       | mA     |

| R <sub>VANA_RPD</sub>      | VANA sleep mode pull-down resistor                                                                                                                                                                                              | _    | 1.0                 | _        | kΩ     |

| t <sub>VANA</sub>          | VANA rise time (CL = 47 nF ceramic X7R only)                                                                                                                                                                                    | _    | _                   | 400      | μs     |

| ADC1-A, ADC1-B             |                                                                                                                                                                                                                                 |      | '                   | 1        |        |

| CTn <sub>(LEAKAGE)</sub>   | Cell terminal input leakage current (except in SLEEP mode when cell balancing is ON)                                                                                                                                            | _    | 10                  | _        | nA     |

| CTn <sub>(FV)</sub>        | Cell terminal input current - functional verification                                                                                                                                                                           | _    | 0.365               | _        | mA     |

| CT <sub>N</sub>            | Cell terminal input current during conversion                                                                                                                                                                                   | _    | 50                  | _        | nA     |

| R <sub>PD</sub>            | Cell terminal open load detection pull-down resistor                                                                                                                                                                            | _    | 950                 | _        | Ω      |

| V <sub>VPWR_RES</sub>      | VPWR terminal measurement resolution                                                                                                                                                                                            | _    | 2.44141             | _        | mV/LSB |

| V <sub>VPWR RNG</sub>      | VPWR terminal measurement range                                                                                                                                                                                                 | 9.6  | _                   | 75       | V      |

| VPWR <sub>TERM_ERR</sub>   | VPWR terminal measurement accuracy                                                                                                                                                                                              | -0.5 | _                   | 0.5      | %      |

| V <sub>CT_RNG</sub>        | ADC differential input voltage range for CTn to CTn-1                                                                                                                                                                           | 0.0  | _                   | 4.85     | V      |

| V <sub>CT_ANx_RES</sub>    | Cell voltage and ANx resolution in 15-bit MEAS xxxx registers                                                                                                                                                                   | _    | 152.58789           | _        | μV/LSB |

| V <sub>ANX_RATIO_RES</sub> | ANx resolution in 15-bit MEAS_xxxx registers in ratiometric mode                                                                                                                                                                | _    | VCOM.<br>(30.51758) | _        | μV/LSB |

| V <sub>ERR33RT</sub>       | Cell voltage measurement error V <sub>CELL</sub> = 3.3 V, T <sub>A</sub> = 25 °C                                                                                                                                                | -0.8 | ±0.4                | 0.8      | mV     |

| V <sub>ERR</sub>           | Cell voltage measurement error 0.1 V $\leq$ V <sub>CELL</sub> $\leq$ 4.8 V, $-40$ °C $\leq$ T <sub>A</sub> $\leq$ 105 °C (or $-40$ °C $\leq$ T <sub>J</sub> $\leq$ 125 °C)                                                      | _    | ±0.7                | _        | mV     |

| V <sub>ERR_1</sub>         | Cell voltage measurement error $0 \text{ V} \le \text{V}_{\text{CELL}} \le 1.5 \text{ V}, -40 \text{ °C} \le \text{T}_{\text{A}} \le 60 \text{ °C} \text{ (or } -40 \text{ °C} \le \text{T}_{\text{J}} \le 85 \text{ °C})$      | _    | ±0.4                | _        | mV     |

| V <sub>ERR_2</sub>         | Cell voltage measurement error<br>$1.5 \text{ V} \le \text{V}_{\text{CELL}} \le 2.7 \text{ V}, -40 \text{ °C} \le \text{T}_{\text{A}} \le 60 \text{ °C} \text{ (or } -40 \text{ °C} \le \text{T}_{\text{J}} \le 85 \text{ °C)}$ | _    | ±0.4                | _        | mV     |

| V <sub>ERR_3</sub>         | Cell voltage measurement error<br>$2.7 \text{ V} \le \text{V}_{\text{CELL}} \le 3.7 \text{ V}, -40 \text{ °C} \le \text{T}_{\text{A}} \le 60 \text{ °C} \text{ (or } -40 \text{ °C} \le \text{T}_{\text{J}} \le 85 \text{ °C)}$ | _    | ±0.5                | _        | mV     |

| V <sub>ERR_4</sub>         | Cell voltage measurement error<br>$3.7 \text{ V} \le \text{V}_{\text{CELL}} \le 4.3 \text{ V}, -40 \text{ °C} \le \text{T}_{\text{A}} \le 60 \text{ °C} \text{ (or } -40 \text{ °C} \le \text{T}_{\text{J}} \le 85 \text{ °C)}$ | _    | ±0.7                | _        | mV     |

| V <sub>ERR_5</sub>         | Cell voltage measurement error<br>$1.5~\rm V \le V_{CELL} \le 4.5~\rm V, -40~^{\circ}C \le T_A \le 105~^{\circ}C$ (or $-40~^{\circ}C \le T_J \le 125~^{\circ}C$ )                                                               | _    | ±0.7                | _        | mV     |

| V <sub>ANX_ERR</sub>       | Magnitude of ANx error in the entire measurement range: Ratiometric measurement Absolute measurement after soldering and aging, input in the range [1.0, 4.5] V                                                                 | _    | _                   | 16<br>10 | mV     |

|                            | Absolute measurement after soldering and aging, input in the range [0, 4.85] V, for −40 °C < T <sub>A</sub> < 60 °C)  Absolute measurement after soldering and aging, input in the                                              | -8.0 | _                   | 8.0      |        |

|                            |                                                                                                                                                                                                                                 |      |                     |          |        |

Table 8. Static and dynamic electrical characteristics...continued

Characteristics noted under conditions 9.6 V  $\leq$  V<sub>PWR</sub>  $\leq$  63 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C, GND = 0 V, unless otherwise stated. Typical values refer to V<sub>PWR</sub> = 56 V, T<sub>A</sub> = 25 °C, unless otherwise noted.

| Symbol                       | Parameter                                                              | Min  | Тур    | Max | Unit   |

|------------------------------|------------------------------------------------------------------------|------|--------|-----|--------|

| t <sub>VCONV</sub>           | Single channel net conversion time                                     |      |        |     | μs     |

|                              | 13-bit resolution                                                      |      | 6.77   |     |        |

|                              | 14-bit resolution                                                      | _    | 9.43   | _   |        |

|                              | 15-bit resolution                                                      | _    | 14.75  |     |        |

|                              | 16-bit resolution                                                      | _    | 25.36  | _   |        |

| $V_{V\_NOISE}$               | Conversion noise                                                       |      |        |     | μVrms  |

|                              | 13-bit resolution                                                      | _    | 1800   | _   |        |

|                              | 14-bit resolution                                                      | -    | 1000   | _   |        |

|                              | 15-bit resolution                                                      | _    | 600    |     |        |

|                              | 16-bit resolution                                                      | _    | 400    |     |        |

| ADC2/current sen             | se module                                                              |      |        |     |        |

| V <sub>INC</sub>             | ISENSE+/ISENSE- input voltage (reference to AGND)                      | -300 | _      | 300 | mV     |

| $V_{IND}$                    | ISENSE+/ISENSE- differential input voltage range                       | -150 | _      | 150 | mV     |

| V <sub>ISENSEX(OFFSET)</sub> | ISENSE+/ISENSE- input voltage offset error                             | _    | _      | 0.5 | μV     |

| I <sub>SENSEX(BIAS)</sub>    | ISENSE+/ISENSE- input bias current                                     | -100 | _      | 100 | nA     |

| I <sub>SENSE(DIF)</sub>      | ISENSE+/ISENSE- differential input bias current                        | -5.0 | _      | 5.0 | nA     |

| I <sub>GAINERR</sub>         | ISENSE error including nonlinearities                                  | -0.5 | _      | 0.5 | %      |

| I <sub>ISENSE_OL</sub>       | ISENSE open load injected current                                      | _    | 130    | _   | μA     |

| V <sub>ISENSE OL</sub>       | ISENSE open load detection threshold                                   |      | 460    | _   | mV     |

| V <sub>2RES</sub>            | Current sense user register resolution                                 |      | 0.6    | _   | μV/LSB |

| V <sub>PGA_SAT</sub>         | PGA saturation half-range                                              |      |        |     | mV     |

| . 66                         | Gain = 256                                                             | _    | 4.9    |     |        |

|                              | Gain = 64                                                              | _    | 19.5   |     |        |

|                              | Gain = 16                                                              | _    | 78.1   |     |        |

|                              | Gain = 4                                                               | -    | 150.0  | -   |        |

| V <sub>PGA_ITH</sub>         | Voltage threshold for PGA gain increase                                |      |        |     | mV     |

|                              | Gain = 256                                                             | _    | _      | _   |        |

|                              | Gain = 64                                                              | -    | 2.344  | _   |        |

|                              | Gain = 16                                                              | _    | 9.375  |     |        |

|                              | Gain = 4                                                               | _    | 37.50  | _   |        |

| $V_{PGA\_DTH}$               | Voltage threshold for PGA gain decrease                                |      |        |     | mV     |

|                              | Gain = 256                                                             | _    | 4.298  | _   |        |

|                              | Gain = 64                                                              | -    | 17.188 | _   |        |

|                              | Gain = 16                                                              | _    | 68.750 | _   |        |

|                              | Gain = 4                                                               |      | _      |     |        |

| t <sub>AZC_SETTLE</sub>      | Time to perform auto-zero procedure after enabling the current channel | _    | 200    | _   | μs     |

| t <sub>ICONV</sub>           | ADC conversion time including PGA settling time                        |      |        |     | μs     |

|                              | 13 bit resolution                                                      | -    | 19.00  | -   |        |

|                              | 14 bit resolution                                                      | -    | 21.67  | _   |        |

|                              | 15 bit resolution                                                      | -    | 27.00  | _   |        |

|                              | 16 bit resolution                                                      |      | 37.67  |     |        |

| V <sub>I_NOISE</sub>         | Noise error at 16-bit conversion                                       |      | 3.01   | -   | μVrms  |

| V <sub>I_NOISE</sub>         | Noise error at 13-bit conversion                                       |      | 8.33   |     | μVrms  |

| ADC <sub>CLK</sub>           | ADC2 and ADC1-A,B clocking frequency                                   | -    | 6.0    | _   | MHz    |

Table 8. Static and dynamic electrical characteristics...continued

Characteristics noted under conditions 9.6 V  $\leq$  V<sub>PWR</sub>  $\leq$  63 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C, GND = 0 V, unless otherwise stated. Typical values refer to V<sub>PWR</sub> = 56 V, T<sub>A</sub> = 25 °C, unless otherwise noted.

| Symbol                    | Parameter                                                                                                                                                                                         | Min  | Тур            | Max  | Unit   |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------|------|--------|

| Cell balance drive        | rs                                                                                                                                                                                                |      |                |      |        |

| V <sub>DS(CLAMP)</sub>    | Cell balance driver VDS active clamp voltage                                                                                                                                                      | _    | 11             | _    | V      |

| V <sub>OUT(FLT_TH)</sub>  | Output fault detection voltage threshold Balance off (open load) Balance on (shorted load)                                                                                                        | _    | 0.55           | _    | V      |

| R <sub>PD_CB</sub>        | Output OFF open load detection pull-down resistor Balance off, open load detect disabled                                                                                                          | _    | 2.0            | _    | kΩ     |

| I <sub>OUT(LKG)</sub>     | Output leakage current  Balance off, open load detect disabled at V <sub>DS</sub> = 4.0 V                                                                                                         | _    | _              | 1.0  | μΑ     |

| R <sub>DS(on)</sub>       | Drain-to-source on resistance $I_{OUT} = 300 \text{ mA}, T_J = 105 ^{\circ}\text{C}$ $I_{OUT} = 300 \text{ mA}, T_J = 25 ^{\circ}\text{C}$ $I_{OUT} = 300 \text{ mA}, T_J = -40 ^{\circ}\text{C}$ |      | <br>0.5<br>0.4 | 0.80 | Ω      |

| I <sub>LIM_CB</sub>       | Driver current limitation                                                                                                                                                                         | 310  | _              | 950  | mA     |

| t <sub>ON</sub>           | Cell balance driver turn on $R_L=15\;\Omega$                                                                                                                                                      | _    | 350            | _    | μs     |

| t <sub>OFF</sub>          | Cell balance driver turn off $R_L = 15 \; \Omega$                                                                                                                                                 | _    | 200            | _    | μs     |

| t <sub>BAL_DEGLICTH</sub> | Short/open detect filter time                                                                                                                                                                     | _    | 20             | _    | μs     |

| Internal temperatu        | re measurement                                                                                                                                                                                    | -    | · ·            |      |        |

| IC_TEMP1_ERR              | IC temperature measurement error                                                                                                                                                                  | -3.0 | _              | 3.0  | K      |

| IC_TEMP1_RES              | IC temperature resolution                                                                                                                                                                         | _    | 0.032          | _    | K/LSB  |

| TSD_TH                    | Thermal shutdown                                                                                                                                                                                  | _    | 170            | _    | °C     |

| TSD_HYS                   | Thermal shutdown hysteresis                                                                                                                                                                       | _    | 10             | _    | °C     |

| Default operationa        | al parameters                                                                                                                                                                                     |      | l              |      |        |

| V <sub>CTOV(TH)</sub>     | Cell overvoltage threshold (8 bits), typical value is default value after RESET                                                                                                                   | 0.0  | 4.2            | 5.0  | V      |

| V <sub>CTOV(RES)</sub>    | Cell overvoltage threshold resolution                                                                                                                                                             | _    | 19.53125       | _    | mV/LSB |

| V <sub>CTUV(TH)</sub>     | Cell undervoltage threshold (8 bits), typical value is default value after RESET                                                                                                                  | 0.0  | 2.5            | 5.0  | V      |

| V <sub>CTUV(RES)</sub>    | Cell undervoltage threshold resolution                                                                                                                                                            | _    | 19.53125       | _    | mV/LSB |

| $V_{GPIO\_OT(TH)}$        | GPIOx configured as ANx input overtemperature threshold after RESET                                                                                                                               | _    | 1.16           | _    | V      |

| V <sub>GPIO_OT(RES)</sub> | Temperature voltage threshold resolution                                                                                                                                                          | _    | 4.8828125      | _    | mV/LSB |

| $V_{GPIO\_UT(TH)}$        | GPIOx configured as ANx input undertemperature threshold after RESET                                                                                                                              | _    | 3.82           | _    | V      |

| V <sub>GPIO_UT(RES)</sub> | Temperature voltage threshold resolution                                                                                                                                                          | _    | 4.8828125      | _    | mV/LSB |

| General purpose i         | nput/output GPIOx                                                                                                                                                                                 |      |                |      |        |

| V <sub>IH</sub>           | Input high-voltage (3.3 V compatible)                                                                                                                                                             | 2.0  | _              | _    | V      |

| V <sub>IL</sub>           | Input low-voltage (3.3 V compatible)                                                                                                                                                              | _    | _              | 1.0  | V      |

| V <sub>HYS</sub>          | Input hysteresis                                                                                                                                                                                  | _    | 100            | _    | mV     |

| I <sub>IL</sub>           | Input leakage current Pins tristate, V <sub>IN</sub> = V <sub>COM</sub> or AGND                                                                                                                   | -100 | _              | 100  | nA     |

PB\_MC33771C

All information provided in this document is subject to legal disclaimers.

Table 8. Static and dynamic electrical characteristics...continued

Characteristics noted under conditions 9.6 V  $\leq$  V<sub>PWR</sub>  $\leq$  63 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C, GND = 0 V, unless otherwise stated. Typical values refer to V<sub>PWR</sub> = 56 V, T<sub>A</sub> = 25 °C, unless otherwise noted.

| Symbol                     | Parameter                                                                                                                    | Min                    | Тур  | Max              | Unit |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------------------|------|

| IDL                        | Differential Input Leakage Current GPIO 5,6 GPIO 5,6 configured as digital inputs for current measurement                    | -30                    | _    | 30               | nA   |

| V <sub>OH</sub>            | Output high-voltage I <sub>OH</sub> = −0.5 mA                                                                                | V <sub>COM</sub> - 0.8 | _    | _                | V    |

| V <sub>OL</sub>            | Output low-voltage I <sub>OL</sub> = +0.5 mA                                                                                 | _                      | _    | 0.8              | V    |

| V <sub>ADC</sub>           | Analog ADC input voltage range for ratiometric measurements                                                                  | AGND                   | _    | V <sub>COM</sub> | V    |

| V <sub>OL(TH)</sub>        | Analog input open pin detect threshold                                                                                       | _                      | 0.15 | _                | V    |

| R <sub>OPENPD</sub>        | Internal open detection pull-down resistor                                                                                   | _                      | 5.0  | _                | kΩ   |

| t <sub>GPIO0_WU</sub>      | GPIO0 WU de-glitch filter                                                                                                    | _                      | 50   | _                | μs   |

| t <sub>GPIO0_FLT</sub>     | GPIO0 daisy chain de-glitch filter both edges                                                                                | _                      | 20   | _                | μs   |

| t <sub>GPIO2_</sub> soc    | GPIO2 convert trigger de-glitch filter                                                                                       | _                      | 2.0  | _                | μs   |

| t <sub>GPIOx_DIN</sub>     | GPIOx configured as digital input de-glitch filter                                                                           | 2.5                    | _    | 5.6              | μs   |

| Reset input                | ·                                                                                                                            |                        | -    |                  |      |

| V <sub>IH_RST</sub>        | Input high-voltage (3.3 V compatible)                                                                                        | 2.0                    | _    | _                | V    |

| $V_{IL\_RST}$              | Input low-voltage (3.3 V compatible)                                                                                         | _                      | _    | 1.0              | V    |

| V <sub>HYS</sub>           | Input hysteresis                                                                                                             | _                      | 0.6  | _                | V    |

| t <sub>RESETFLT</sub>      | RESET de-glitch filter                                                                                                       | _                      | 100  | _                | μs   |

| R <sub>RESET_PD</sub>      | Input logic pull down (RESET)                                                                                                |                        | 100  | _                | kΩ   |

| SPI_COM_EN inpu            | ut                                                                                                                           |                        |      |                  |      |

| V <sub>IH</sub>            | Input high-voltage (3.3 V compatible)                                                                                        | 2.0                    | _    | _                | V    |

| V <sub>IL</sub>            | Input low-voltage (3.3 V compatible)                                                                                         | _                      | _    | 1.0              | V    |

| V <sub>HYS</sub>           | Input hysteresis                                                                                                             | _                      | 450  | _                | mV   |

| R <sub>SPI_COM_EN_PD</sub> | Input pull-down resistor (SPI_COM_EN)                                                                                        | _                      | 100  | _                | kΩ   |

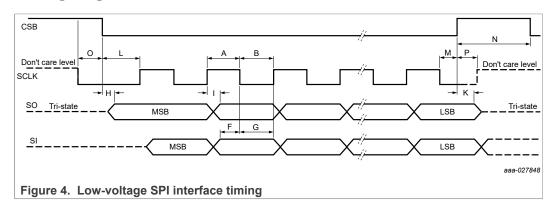

| Digital interface          |                                                                                                                              |                        | 1    |                  |      |

| V <sub>FAULT_HA</sub>      | FAULT output (high active, IOH = 1.0 mA)                                                                                     | _                      | 4.9  | _                | V    |

| I <sub>FAULT CL</sub>      | FAULT output current limit                                                                                                   | 3.0                    | _    | 40               | mA   |

| R <sub>FAULT PD</sub>      | FAULT output pull-down resistance                                                                                            | _                      | 100  | _                | kΩ   |

| -<br>V <sub>IH_СОММ</sub>  | Voltage threshold to detect the input as high SI/RDTX_IN+, SCLK/RDTX_IN-, CSB, SDA, SCL (NOTE: needs to be 3.3 V compatible) | _                      | _    | 2.0              | V    |

| V <sub>IL_COMM</sub>       | Voltage threshold to detect the input as low SI/RDTX_IN+, SCLK/RDTX_IN-, CSB, SDA, SCL                                       | 0.8                    | _    | _                | V    |

| V <sub>HYS</sub>           | Input hysteresis SI/RDTX_IN+, SCLK/RDTX_IN-, CSB, SDA, SCL                                                                   | _                      | 80   | _                | mV   |

| I <sub>LOGIC_</sub> ss     | Sleep state input logic current<br>CSB                                                                                       | -100                   | _    | 100              | nA   |

| R <sub>SCLK_PD</sub>       | Input logic pull-down resistance (SCLK/RDTX_IN-, SI/RDTX_IN+)                                                                | _                      | 20   | _                | kΩ   |

| $R_{I\_PU}$                | Input logic pull-up resistance to V <sub>COM</sub> (CSB, SDA, SCL)                                                           | _                      | 100  | _                | kΩ   |

| I <sub>SO_TRI</sub>        | Tristate SO input current 0 V to V <sub>COM</sub>                                                                            | -2.0                   | _    | 2.0              | μA   |

| V <sub>SO_HIGH</sub>       |                                                                                                                              |                        | _    | _                | V    |

PB\_MC33771C

All information provided in this document is subject to legal disclaimers.

Table 8. Static and dynamic electrical characteristics...continued

Characteristics noted under conditions 9.6 V  $\leq$  V<sub>PWR</sub>  $\leq$  63 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C, GND = 0 V, unless otherwise stated. Typical values refer to V<sub>PWR</sub> = 56 V, T<sub>A</sub> = 25 °C, unless otherwise noted.

| Symbol                | Parameter                                                                                                                          | Min | Тур    | Max      | Unit |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|--------|----------|------|

| V <sub>SO_LOW</sub>   | SO, SDA, SLK low-state output voltage with I <sub>SO(HIGH)</sub> = −2.0 mA                                                         | _   | _      | 0.4      | V    |

| CSB <sub>WU_FLT</sub> | CSB wake-up de-glitch filter, low to high transition                                                                               | _   | _      | 80       | μs   |

| System timing         |                                                                                                                                    |     |        |          |      |

| CELL_CONV             | Time needed to acquire all 14 cell voltages and the current after an                                                               |     |        |          | μs   |

|                       | on-demand conversion                                                                                                               |     |        |          |      |

|                       | 13-bit resolution                                                                                                                  | _   | 59     | _        |      |

|                       | 14-bit resolution                                                                                                                  | _   | 80     | _        |      |

|                       | 15-bit resolution                                                                                                                  | _   | 123    | _        |      |

|                       | 16-bit resolution                                                                                                                  | _   | 208    | _        |      |

| SYNC                  | V/I synchronization time                                                                                                           |     |        |          | μs   |

|                       | ADC1-A,B at 13 bit, ADC2 at 13 bit                                                                                                 | _   | 48.16  | _        |      |

|                       | ADC1-A,B at 14 bit, ADC2 at 13 bit                                                                                                 | _   | 53.50  | _        |      |

|                       | ADC1-A,B at 15 bit, ADC2 at 13 bit                                                                                                 | _   | 64.16  | _        |      |

|                       | ADC1-A,B at 16 bit, ADC2 at 13 bit                                                                                                 | -   | 85.50  | _        |      |

| SYNC                  | V/I synchronization time                                                                                                           |     |        |          | μs   |