Bezahlverfahren

CPLD ispLSI® 1000 Family 6K Gates 128 Macro Cells 60MHz 5V 84-Pin CPGA

CPGAHersteller:

Herstellerteil #:

5962-9308501MXC

Datenblatt:

Shipping Restrictions:

This product may require additional documentation to export from the United States.

Mounting Style:

SMD/SMT

Operating Supply Voltage:

5 V

Number of Macrocells:

128 Macrocell

EDA/CAD Modelle:

Bitte füllen Sie das kurze Formular unten aus und wir werden Ihnen umgehend ein Angebot zukommen lassen..

| Product Category | CPLD - Complex Programmable Logic Devices | Shipping Restrictions | This product may require additional documentation to export from the United States. |

| Mounting Style | SMD/SMT | Operating Supply Voltage | 5 V |

| Number of Macrocells | 128 Macrocell | Number of I/Os | 64 I/O |

| Supply Voltage - Max | 5.5 V | Supply Voltage - Min | 4.5 V |

| Minimum Operating Temperature | - 55 C | Maximum Operating Temperature | + 125 C |

| Maximum Operating Frequency | 60 MHz | Propagation Delay - Max | 20 ns |

| Height | 3.68 mm | Length | 29.97 mm |

| Number of Gates | 6000 | Number of Logic Array Blocks - LABs | 32 |

| Operating Supply Current | 220 mA | Product Type | CPLD - Complex Programmable Logic Devices |

| Factory Pack Quantity | 1 | Subcategory | Programmable Logic ICs |

| Width | 29.97 mm | Unit Weight | 0.488544 oz |

After-Sales- und Abwicklungsbezogen

Zahlung

Zahlung

Bezahlverfahren

Für alternative Zahlungskanäle kontaktieren Sie uns bitte unter:

[email protected] Versand & Verpackung

Versand & Verpackung

Versandart

AVAQ bestimmt und verpackt alle Geräte auf der Grundlage der Schutzanforderungen gegen elektrostatische Entladung (ESD) und Feuchtigkeitsempfindlichkeit (MSL)..

Garantie

Garantie

365-Tage-Produkt

Qualitätsgarantie

Wir versprechen, 365 Tage Qualitätssicherung für alle unsere Produkte zu bieten.

| Menge. | Einzelpreis | Ext. Preis |

|---|---|---|

| 1+ | - | - |

Die unten angegebenen Preise dienen nur als Referenz.

Alle Stücklisten (BOM) können per E-Mail gesendet werden an ![]() [email protected],

oder füllen Sie das folgende Formular aus, um ein Angebot für 5962-9308501MXC zu erhalten. Garantierte Angebote innerhalb

[email protected],

oder füllen Sie das folgende Formular aus, um ein Angebot für 5962-9308501MXC zu erhalten. Garantierte Angebote innerhalb

![]() 12 Std.

12 Std.

LCMXO2-1200HC-4TG100I

LATTICE

1000+ $3,419

LCMXO2-1200HC-4TG100C

LATTICE

1000+ $2,604

LC4032V-75TN48C

Lattice

High Performance E2 CMOS PLD Generic Array Logic

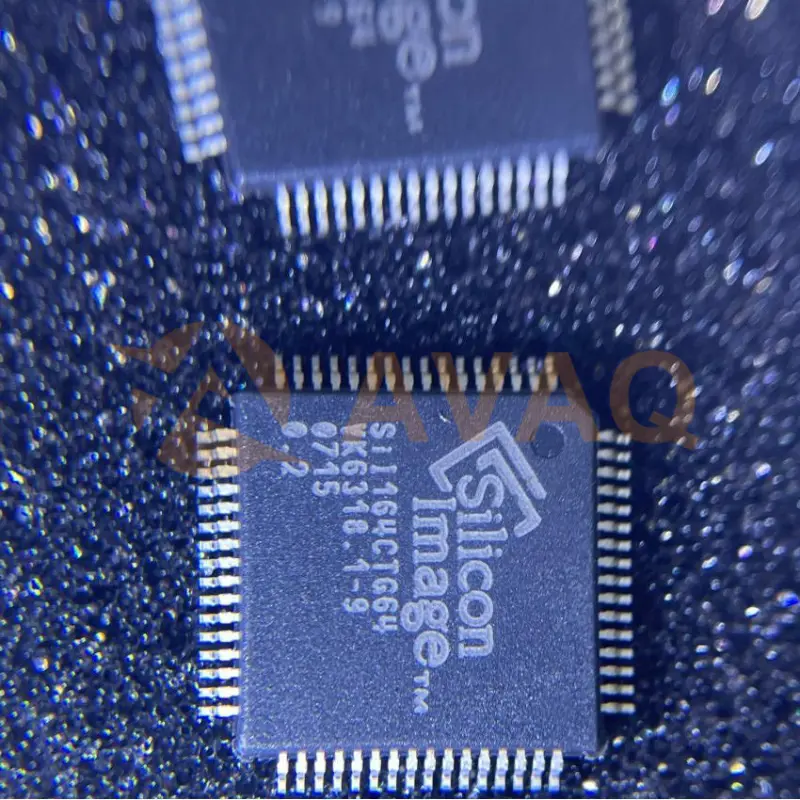

SiI164CTG64

Lattice

TQFP package Transmitter with 2 transmitters

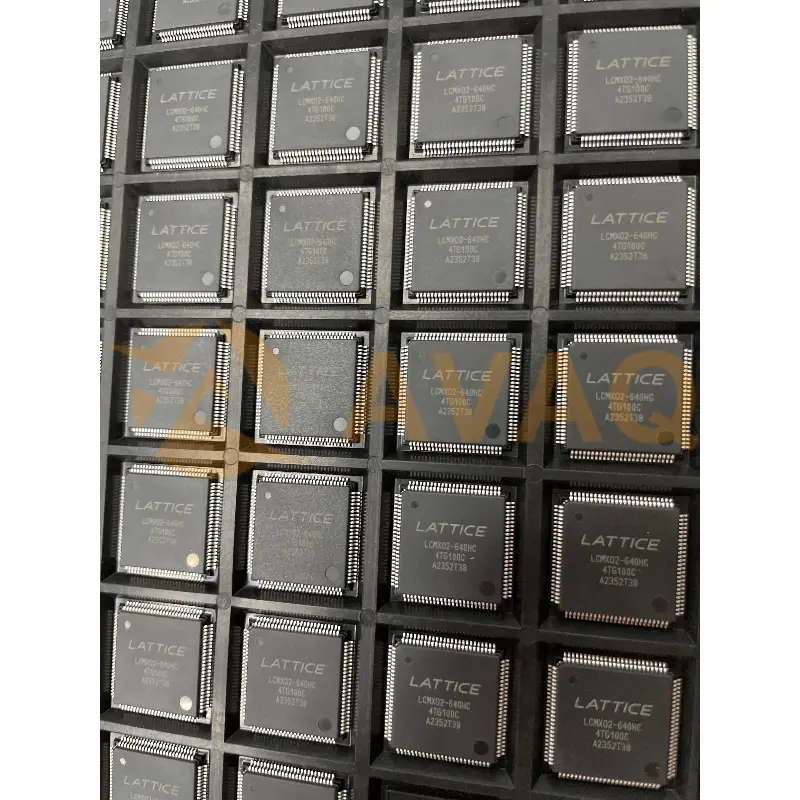

LCMXO2-640HC-4TG100C

Lattice

ROHS Programmable Logic Device (CPLDs/FPGAs) 640 80 TQFP-100(14x14) LCMXO2-640HC-4TG100C