Bezahlverfahren

Programmable Logic Device with 24,576 CLBs and 1,000,000 Gates in a PQFP208 Package

PQFP-208Hersteller:

MICROSEMI CORP

Herstellerteil #:

A3P1000-PQ208M

Datenblatt:

Part Life Cycle Code:

Obsolete

ECCN Code:

3A001.A.2.C

HTS Code:

8542.39.00.01

Clock Frequency-Max:

350 MHz

EDA/CAD Modelle:

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for A3P1000-PQ208M, guaranteed quotes back within

[email protected],

or fill below form to Quote for A3P1000-PQ208M, guaranteed quotes back within

![]() 12hr.

12hr.

Bitte füllen Sie das kurze Formular unten aus und wir werden Ihnen umgehend ein Angebot zukommen lassen..

Operating at a supply voltage of 1.2V, the A3P1000-PQ208M is designed for energy efficiency, making it suitable for battery-operated devices where power consumption is a critical factor. Additionally, this FPGA includes robust security features to protect sensitive intellectual property, including non-volatile design security, design encryption, and tamper detection capabilities. These security measures help ensure that your designs are safe from unauthorized access and potential threats

High Capacity 15 K to 1 M System Gates Up to 144 Kbits of True Dual-Port SRAM Up to 300 User I/OsReprogrammable Flash Technology 130-nm, 7-Layer Metal (6 Copper), Flash-Based CMOSProcess Instant On Level 0 Support Single-Chip Solution Retains Programmed Design when Powered OffHigh Performance 350 MHz System Performance 3.3 V, 66 MHz 64-Bit PCIIn-System Programming (ISP) and Security ISP Using On-Chip 128-Bit Advanced Encryption Standard(AES) Decryption (except ARM-enabled ProASIC3 devices)via JTAG (IEEE 1532compliant) FlashLock to Secure FPGA ContentsLow Power Core Voltage for Low Power Support for 1.5 V-Only Systems Low-Impedance Flash SwitchesHigh-Performance Routing Hierarchy Segmented, Hierarchical Routing and Clock StructureAdvanced I/O 700 Mbps DDR, LVDS-Capable I/Os (A3P250 and above) 1.5 V, 1.8 V, 2.5 V, and 3.3 V Mixed-Voltage Operation Wide Range Power Supply Voltage Support per JESD8-B,Allowing I/Os to Operate from 2.7 V to 3.6 V Bank-Selectable I/O Voltagesup to 4 Banks per Chip Single-Ended I/O Standards: LVTTL, LVCMOS 3.3 V /2.5 V / 1.8 V / 1.5 V, 3.3 V PCI / 3.3 V PCI-X and LVCMOS2.5 V / 5.0 V Input Differential I/O Standards: LVPECL, LVDS, B-LVDS, andM-LVDS (A3P250 and above) I/O Registers on Input, Output, and Enable Paths Hot-Swappable and Cold Sparing I/Os Programmable Output Slew Rate and Drive Strength Weak Pull-Up/-Down IEEE 1149.1 (JTAG) Boundary Scan Test Pin-Compatible Packages across the ProASIC3 FamilyClock Conditioning Circuit (CCC) and PLL Six CCC Blocks, One with an Integrated PLL Configurable Phase-Shift, Multiply/Divide, Delay Capabilitiesand External Feedback Wide Input Frequency Range (1.5 MHz to 350 MHz)Embedded Memory 1 Kbit of FlashROM User Nonvolatile Memory SRAMs and FIFOs with Variable-Aspect-Ratio 4,608-Bit RAMBlocks (1, 2, 4, 9, and 18 organizations) True Dual-Port SRAM (except 18)ARM Processor Support in ProASIC3 FPGAs M1 ProASIC3 DevicesARMCortex-M1 Soft ProcessorAvailable with or without Debug

| Part Life Cycle Code | Obsolete | Reach Compliance Code | |

| ECCN Code | 3A001.A.2.C | HTS Code | 8542.39.00.01 |

| Clock Frequency-Max | 350 MHz | JESD-30 Code | S-PQFP-G208 |

| JESD-609 Code | e0 | Length | 28 mm |

| Moisture Sensitivity Level | 3 | Number of CLBs | 24576 |

| Number of Equivalent Gates | 1000000 | Number of Inputs | 154 |

| Number of Logic Cells | 24576 | Number of Outputs | 154 |

| Number of Terminals | 208 | Operating Temperature-Max | 125 °C |

| Operating Temperature-Min | -55 °C | Organization | 24576 CLBS, 1000000 GATES |

| Peak Reflow Temperature (Cel) | 225 | Power Supplies | 1.5,1.5/3.3 V |

| Programmable Logic Type | FIELD PROGRAMMABLE GATE ARRAY | Qualification Status | Not Qualified |

| Seated Height-Max | 4.1 mm | Supply Voltage-Max | 1.575 V |

| Supply Voltage-Min | 1.425 V | Supply Voltage-Nom | 1.5 V |

| Surface Mount | YES | Technology | CMOS |

| Temperature Grade | MILITARY | Terminal Finish | TIN LEAD |

| Terminal Form | GULL WING | Terminal Pitch | 0.5 mm |

| Terminal Position | QUAD | Time@Peak Reflow Temperature-Max (s) | 20 |

| Width | 28 mm |

After-Sales- und Abwicklungsbezogen

Zahlung

Zahlung

Bezahlverfahren

Für alternative Zahlungskanäle kontaktieren Sie uns bitte unter:

[email protected] Versand & Verpackung

Versand & Verpackung

Versandart

AVAQ bestimmt und verpackt alle Geräte auf der Grundlage der Schutzanforderungen gegen elektrostatische Entladung (ESD) und Feuchtigkeitsempfindlichkeit (MSL)..

Garantie

Garantie

365-Tage-Produkt

Qualitätsgarantie

Wir versprechen, 365 Tage Qualitätssicherung für alle unsere Produkte zu bieten.

| Menge. | Einzelpreis | Ext. Preis |

|---|---|---|

| 1+ | - | - |

Die unten angegebenen Preise dienen nur als Referenz.

C100

Issi

Video ICs 4MP H.265 Video Processor - 64MB DDR2, BGA85, 5mm x 6mm

NE555

Texas Instruments

100kHz operation frequency with low power consumption for long-lasting performance

CD4017

Onsemi

Compact digital counter for precision measurement application

74LS04

Onsemi

High-quality die for professional use only, unsurfaced and untested

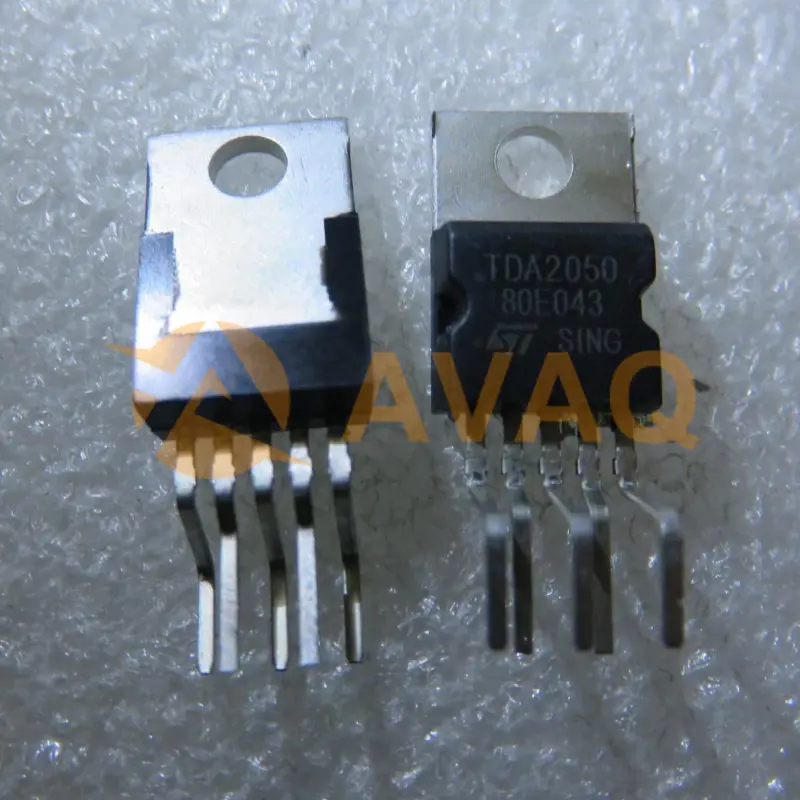

TDA2050

Stmicroelectronics

Effortlessly drives your speakers with crystal-clear sound and robust power