Bezahlverfahren

A3PE3000L-PQ208I - a high-performance FPGA ideal for various applications

PQFP-208Hersteller:

MICROSEMI CORP

Herstellerteil #:

A3PE3000L-PQ208I

Datenblatt:

Part Life Cycle Code:

Transferred

HTS Code:

8542.39.00.01

JESD-30 Code:

S-PQFP-G208

JESD-609 Code:

e0

EDA/CAD Modelle:

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for A3PE3000L-PQ208I, guaranteed quotes back within

[email protected],

or fill below form to Quote for A3PE3000L-PQ208I, guaranteed quotes back within

![]() 12hr.

12hr.

Bitte füllen Sie das kurze Formular unten aus und wir werden Ihnen umgehend ein Angebot zukommen lassen..

Crafted to cater to the evolving demands of modern technology, the A3PE3000L-PQ208I stands out as a reliable and efficient solution for a wide array of applications. Its robust design, coupled with advanced security features, makes it an ideal choice for industries where data protection is paramount. By combining performance, power efficiency, and security in a single package, the A3PE3000L-PQ208I sets a new standard for SoC FPGAs in the market

| Part Life Cycle Code | Transferred | Reach Compliance Code | |

| HTS Code | 8542.39.00.01 | JESD-30 Code | S-PQFP-G208 |

| JESD-609 Code | e0 | Length | 28 mm |

| Moisture Sensitivity Level | 3 | Number of CLBs | 75264 |

| Number of Equivalent Gates | 3000000 | Number of Inputs | 147 |

| Number of Logic Cells | 75264 | Number of Outputs | 147 |

| Number of Terminals | 208 | Operating Temperature-Max | 85 °C |

| Operating Temperature-Min | -40 °C | Organization | 75264 CLBS, 3000000 GATES |

| Peak Reflow Temperature (Cel) | 225 | Power Supplies | 1.2/1.5,1.2/3.3 V |

| Programmable Logic Type | FIELD PROGRAMMABLE GATE ARRAY | Qualification Status | Not Qualified |

| Seated Height-Max | 4.1 mm | Supply Voltage-Max | 1.575 V |

| Supply Voltage-Min | 1.14 V | Supply Voltage-Nom | 1.2 V |

| Surface Mount | YES | Technology | CMOS |

| Temperature Grade | INDUSTRIAL | Terminal Finish | TIN LEAD |

| Terminal Form | GULL WING | Terminal Pitch | 0.5 mm |

| Terminal Position | QUAD | Time@Peak Reflow Temperature-Max (s) | 20 |

| Width | 28 mm |

After-Sales- und Abwicklungsbezogen

Zahlung

Zahlung

Bezahlverfahren

Für alternative Zahlungskanäle kontaktieren Sie uns bitte unter:

[email protected] Versand & Verpackung

Versand & Verpackung

Versandart

AVAQ bestimmt und verpackt alle Geräte auf der Grundlage der Schutzanforderungen gegen elektrostatische Entladung (ESD) und Feuchtigkeitsempfindlichkeit (MSL)..

Garantie

Garantie

365-Tage-Produkt

Qualitätsgarantie

Wir versprechen, 365 Tage Qualitätssicherung für alle unsere Produkte zu bieten.

| Menge. | Einzelpreis | Ext. Preis |

|---|---|---|

| 1+ | - | - |

Die unten angegebenen Preise dienen nur als Referenz.

C100

Issi

Video ICs 4MP H.265 Video Processor - 64MB DDR2, BGA85, 5mm x 6mm

NE555

Texas Instruments

100kHz operation frequency with low power consumption for long-lasting performance

CD4017

Onsemi

Compact digital counter for precision measurement application

74LS04

Onsemi

High-quality die for professional use only, unsurfaced and untested

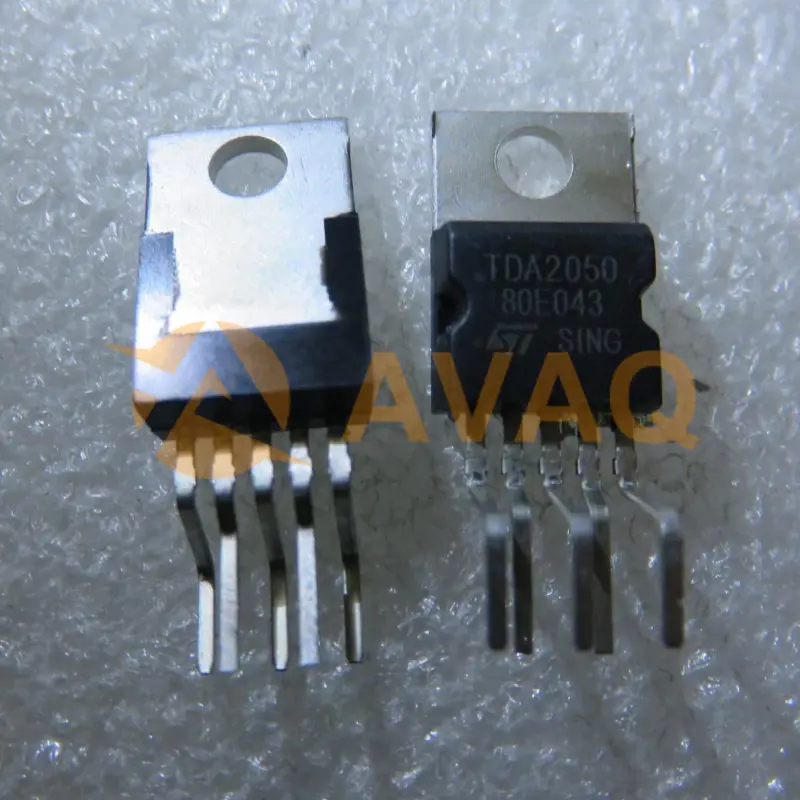

TDA2050

Stmicroelectronics

Effortlessly drives your speakers with crystal-clear sound and robust power