Bezahlverfahren

A3PE600L-FG484M FPGA

FBGAHersteller:

MICROCHIP TECHNOLOGY INC

Herstellerteil #:

A3PE600L-FG484M

Datenblatt:

Part Life Cycle Code:

Active

Reach Compliance Code:

compliant

ECCN Code:

3A001.A.2.C

HTS Code:

8542.39.00.01

EDA/CAD Modelle:

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for A3PE600L-FG484M, guaranteed quotes back within

[email protected],

or fill below form to Quote for A3PE600L-FG484M, guaranteed quotes back within

![]() 12hr.

12hr.

Bitte füllen Sie das kurze Formular unten aus und wir werden Ihnen umgehend ein Angebot zukommen lassen..

In summary, the A3PE600L-FG484M is a cutting-edge FPGA that combines high performance with robust security features. Its extensive system gates, logic elements, and embedded block RAM make it a reliable choice for demanding designs, while its voltage options and IO standards support provide flexibility and ease of integration. Whether you're working on a medium-scale project or a high-density application, this FPGA offers the power and security you need for successful data processing

| Part Life Cycle Code | Active | Reach Compliance Code | compliant |

| ECCN Code | 3A001.A.2.C | HTS Code | 8542.39.00.01 |

| Clock Frequency-Max | 250 MHz | JESD-30 Code | S-PBGA-B484 |

| JESD-609 Code | e0 | Length | 23 mm |

| Moisture Sensitivity Level | 3 | Number of CLBs | 13824 |

| Number of Equivalent Gates | 600000 | Number of Inputs | 270 |

| Number of Logic Cells | 13824 | Number of Outputs | 270 |

| Number of Terminals | 484 | Operating Temperature-Max | 125 °C |

| Operating Temperature-Min | -55 °C | Organization | 13824 CLBS, 600000 GATES |

| Peak Reflow Temperature (Cel) | 225 | Power Supplies | 1.2/1.5,1.2/3.3 V |

| Programmable Logic Type | FIELD PROGRAMMABLE GATE ARRAY | Qualification Status | Not Qualified |

| Seated Height-Max | 2.44 mm | Supply Voltage-Max | 1.575 V |

| Supply Voltage-Min | 1.14 V | Supply Voltage-Nom | 1.2 V |

| Surface Mount | YES | Technology | CMOS |

| Temperature Grade | MILITARY | Terminal Finish | TIN LEAD |

| Terminal Form | BALL | Terminal Pitch | 1 mm |

| Terminal Position | BOTTOM | Time@Peak Reflow Temperature-Max (s) | 20 |

| Width | 23 mm |

After-Sales- und Abwicklungsbezogen

Zahlung

Zahlung

Bezahlverfahren

Für alternative Zahlungskanäle kontaktieren Sie uns bitte unter:

[email protected] Versand & Verpackung

Versand & Verpackung

Versandart

AVAQ bestimmt und verpackt alle Geräte auf der Grundlage der Schutzanforderungen gegen elektrostatische Entladung (ESD) und Feuchtigkeitsempfindlichkeit (MSL)..

Garantie

Garantie

365-Tage-Produkt

Qualitätsgarantie

Wir versprechen, 365 Tage Qualitätssicherung für alle unsere Produkte zu bieten.

| Menge. | Einzelpreis | Ext. Preis |

|---|---|---|

| 1+ | - | - |

Die unten angegebenen Preise dienen nur als Referenz.

C100

Issi

Video ICs 4MP H.265 Video Processor - 64MB DDR2, BGA85, 5mm x 6mm

NE555

Texas Instruments

100kHz operation frequency with low power consumption for long-lasting performance

CD4017

Onsemi

Compact digital counter for precision measurement application

74LS04

Onsemi

High-quality die for professional use only, unsurfaced and untested

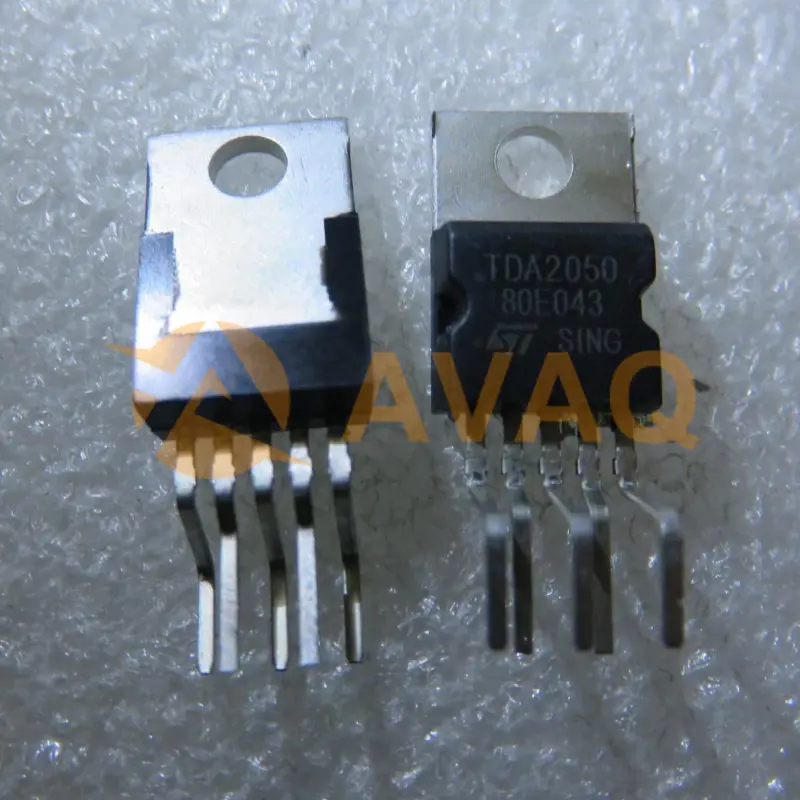

TDA2050

Stmicroelectronics

Effortlessly drives your speakers with crystal-clear sound and robust power