Bezahlverfahren

12ns response time on the 512-cell EE PLD with CMOS technology and PQFP208 package

QFP-208Hersteller:

CYPRESS SEMICONDUCTOR CORP

Herstellerteil #:

CY37512P208-100NI

Datenblatt:

Part Life Cycle Code:

Obsolete

Pin Count:

208

Reach Compliance Code:

not_compliant

HTS Code:

8542.39.00.01

EDA/CAD Modelle:

Senden Sie alle Stücklisten an ![]() [email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für CY37512P208-100NI zu erhalten. Garantierte Antwort innerhalb

[email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für CY37512P208-100NI zu erhalten. Garantierte Antwort innerhalb

![]() 12hr.

12hr.

Bitte füllen Sie das kurze Formular unten aus und wir werden Ihnen umgehend ein Angebot zukommen lassen..

General DescriptionThe Ultra37000™ family of CMOSCPLDs provides a range of high-density programmable logic solutions with unparalleled system performance. The Ultra37000 family is designed to bring the flexibility, ease of use, and performance of the 22V10 to high-density CPLDs. The architecture is based on a number of logic blocks that are connected by a Programmable Interconnect Matrix (PIM).

| Part Life Cycle Code | Obsolete | Pin Count | 208 |

| Reach Compliance Code | not_compliant | HTS Code | 8542.39.00.01 |

| Additional Feature | 512 MACROCELLS; CONFIGURABLE I/O OPERATION WITH 3.3V OR 5V | Architecture | PLA-TYPE |

| Clock Frequency-Max | 80 MHz | In-System Programmable | YES |

| JESD-30 Code | S-PQFP-G208 | JESD-609 Code | e0 |

| JTAG BST | YES | Length | 28 mm |

| Moisture Sensitivity Level | 3 | Number of Dedicated Inputs | 1 |

| Number of I/O Lines | 160 | Number of Inputs | 165 |

| Number of Macro Cells | 512 | Number of Outputs | 160 |

| Number of Terminals | 208 | Operating Temperature-Max | 85 °C |

| Operating Temperature-Min | -40 °C | Organization | 1 DEDICATED INPUTS, 160 I/O |

| Output Function | MACROCELL | Power Supplies | 3.3/5 V |

| Programmable Logic Type | EE PLD | Propagation Delay | 12 ns |

| Qualification Status | Not Qualified | Seated Height-Max | 3.7 mm |

| Supply Voltage-Max | 5.5 V | Supply Voltage-Min | 4.5 V |

| Supply Voltage-Nom | 5 V | Surface Mount | YES |

| Technology | CMOS | Temperature Grade | INDUSTRIAL |

| Terminal Finish | TIN LEAD | Terminal Form | GULL WING |

| Terminal Pitch | 0.5 mm | Terminal Position | QUAD |

| Width | 28 mm |

After-Sales- und Abwicklungsbezogen

Zahlung

Zahlung

Bezahlverfahren

Für alternative Zahlungskanäle kontaktieren Sie uns bitte unter:

[email protected] Versand & Verpackung

Versand & Verpackung

Versandart

AVAQ bestimmt und verpackt alle Geräte auf der Grundlage der Schutzanforderungen gegen elektrostatische Entladung (ESD) und Feuchtigkeitsempfindlichkeit (MSL)..

Garantie

Garantie

365-Tage-Produkt

Qualitätsgarantie

Wir versprechen, 365 Tage Qualitätssicherung für alle unsere Produkte zu bieten.

| Menge. | Einzelpreis | Ext. Preis |

|---|---|---|

| 1+ | - | - |

Die unten angegebenen Preise dienen nur als Referenz.

NE555

Texas Instruments

100kHz operation frequency with low power consumption for long-lasting performance

CD4017

Onsemi

Compact digital counter for precision measurement application

74LS04

Onsemi

High-quality die for professional use only, unsurfaced and untested

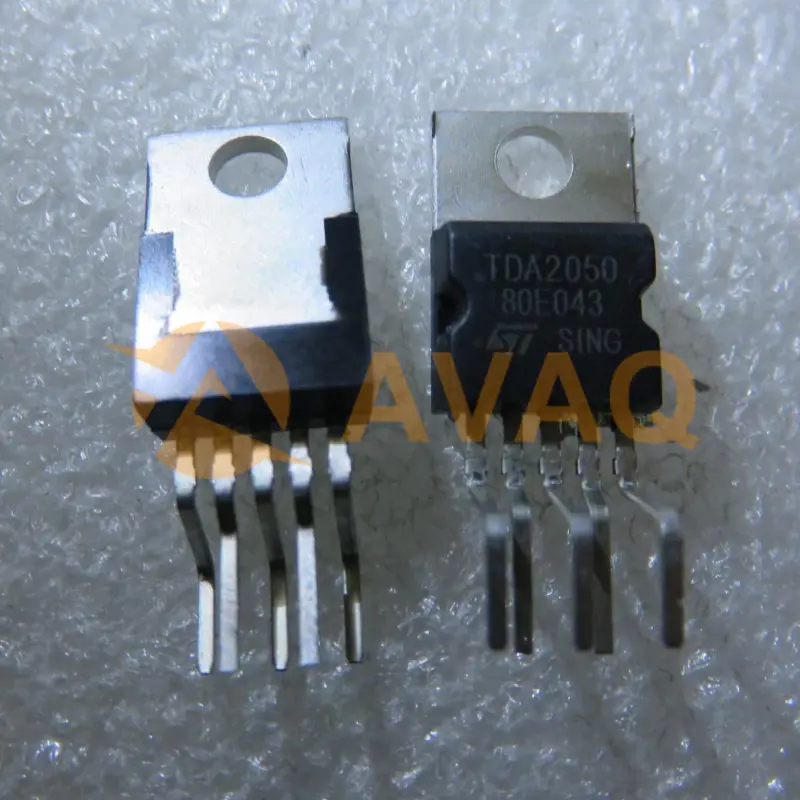

TDA2050

Stmicroelectronics

Effortlessly drives your speakers with crystal-clear sound and robust power

DS1307+

Analog Devices

I2C DIP-8 Real-time Clocks (RTC) ROHS