Bezahlverfahren

Dual Pixel LVDS Display Interface / FPD-Link Transmitter

QFPHersteller:

NS

Herstellerteil #:

DS90C387A

Datenblatt:

Paket/Koffer:

QFP

Produktart:

RoHS:

EDA/CAD Modelle:

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for DS90C387A, guaranteed quotes back within

[email protected],

or fill below form to Quote for DS90C387A, guaranteed quotes back within

![]() 12hr.

12hr.

Bitte füllen Sie das kurze Formular unten aus und wir werden Ihnen umgehend ein Angebot zukommen lassen..

The DS90C387A/DS90CF388A transmitter/receiver pair is designed to support dual pixel data transmission between Host and Flat Panel Display up to QXGA resolutions. The transmitter converts 48 bits (Dual Pixel 24-bit color) of CMOS/TTL data and 3 control bits into 8 LVDS (Low Voltage Differential Signalling) data streams. At a maximum dual pixel rate of 112MHz, LVDS data line speed is 784Mbps, providing a total throughput of 5.7Gbps (714 Megabytes per second).

The LDI chipset is improved over prior generations of FPD-Link devices and offers higher bandwidth support and longer cable drive. To increase bandwidth, the maximum pixel clock rate is increased to 112 MHz and 8 serialized LVDS outputs are provided. Cable drive is enhanced with a user selectable pre-emphasis feature that provides additional output current during transitions to counteract cable loading effects.

The DS90C387A transmitter provides a second LVDS output clock. Both LVDS clocks are identical. This feature supports backward compatibility with the previous generation of FPD-Link Receivers - the second clock allows the transmitter to interface to panels using a 'dual pixel' configuration of two 24-bit or 18-bit FPD-Link receivers.

This chipset is an ideal means to solve EMI and cable size problems for high-resolution flat panel applications. It provides a reliable interface based on LVDS technology that delivers the bandwidth needed for high-resolution panels while maximizing bit times, and keeping clock rates low to reduce EMI and shielding requirements. For more details, please refer to the "Applications Information" section of this datasheet.

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

After-Sales- und Abwicklungsbezogen

Zahlung

Zahlung

Bezahlverfahren

Für alternative Zahlungskanäle kontaktieren Sie uns bitte unter:

[email protected] Versand & Verpackung

Versand & Verpackung

Versandart

AVAQ bestimmt und verpackt alle Geräte auf der Grundlage der Schutzanforderungen gegen elektrostatische Entladung (ESD) und Feuchtigkeitsempfindlichkeit (MSL)..

Garantie

Garantie

365-Tage-Produkt

Qualitätsgarantie

Wir versprechen, 365 Tage Qualitätssicherung für alle unsere Produkte zu bieten.

| Menge. | Einzelpreis | Ext. Preis |

|---|---|---|

| 1+ | - | - |

Die unten angegebenen Preise dienen nur als Referenz.

CP2102

Silicon Laboratories

Integrate seamlessly into your design with our reliable interface I

MAX232

Texas Instruments

This V device features bps data transfer rates and robust ESD protection

W5500

Wiznet

With its comprehensive set of protocols and interfaces, this IC streamlines network development and deploymen

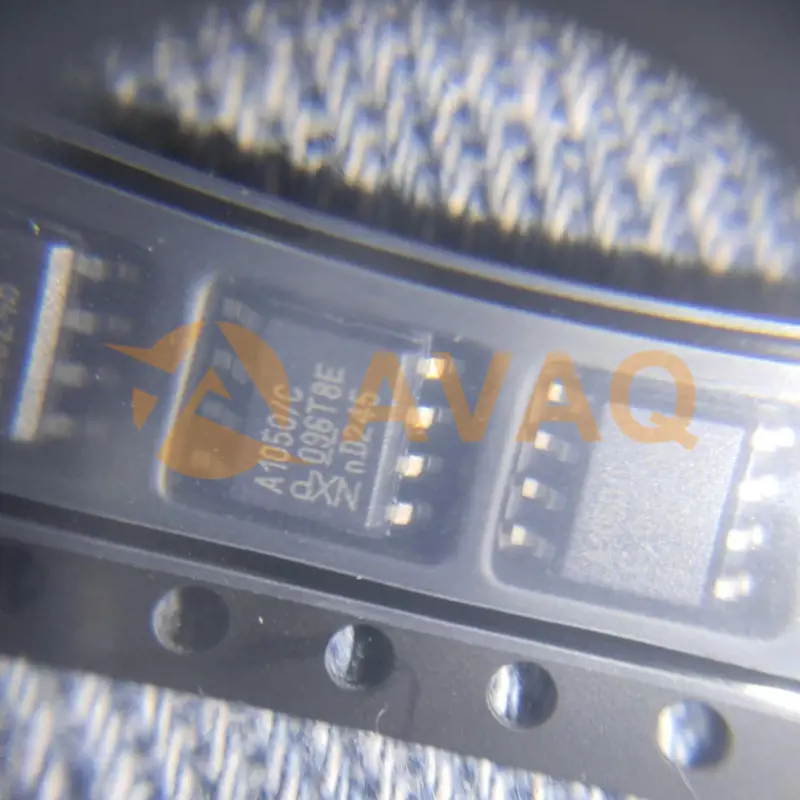

TJA1050

Nxp

Robust and reliable high-speed communication solution for demanding application

RTL2832U

Realtek

High-performance demodulation for DVB-T signals, plug-and-play via US