Bezahlverfahren

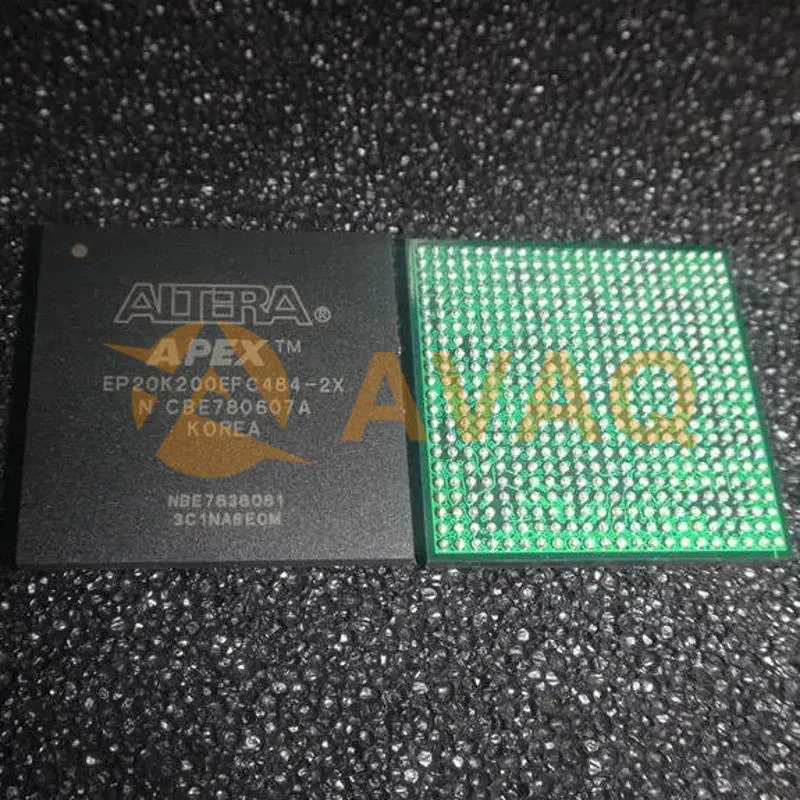

EP20K200EFC484-2X is a Field Programmable Gate Array CPLD with 832 Macro and 376 IOs

FBGA-484Hersteller:

Herstellerteil #:

EP20K200EFC484-2X

Datenblatt:

Series:

APEX 20K EP20K200E

Number Of Logic Elements:

8320 LE

Embedded Memory:

104 kbit

Number Of I/Os:

376 I/O

EDA/CAD Modelle:

Senden Sie alle Stücklisten an ![]() [email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für EP20K200EFC484-2X zu erhalten. Garantierte Antwort innerhalb

[email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für EP20K200EFC484-2X zu erhalten. Garantierte Antwort innerhalb

![]() 12hr.

12hr.

Bitte füllen Sie das kurze Formular unten aus und wir werden Ihnen umgehend ein Angebot zukommen lassen..

The EP20K200EFC484-2X is a cutting-edge Field-Programmable Gate Array (FPGA) from Altera's renowned Stratix family. With a staggering 200,000 logic elements and 6,500 Kbits of embedded memory, this FPGA is a powerhouse of performance and versatility. Its 484-pin FineLine BGA package with a 1.0mm ball pitch ensures a compact yet robust form factor, making it ideal for a wide array of applications across various industries

| Product Category | FPGA - Field Programmable Gate Array | Series | APEX 20K EP20K200E |

| Number of Logic Elements | 8320 LE | Adaptive Logic Modules - ALMs | - |

| Embedded Memory | 104 kbit | Number of I/Os | 376 I/O |

| Supply Voltage - Min | 2.5 V | Supply Voltage - Max | 2.5 V |

| Minimum Operating Temperature | 0 C | Maximum Operating Temperature | + 70 C |

| Mounting Style | SMD/SMT | Packaging | [ "Tray" ] |

| Maximum Operating Frequency | 170 MHz | Moisture Sensitive | Yes |

| Number of Gates | 526000 | Number of Logic Array Blocks - LABs | 832 LAB |

| Operating Supply Voltage | 2.5 V | Product Type | FPGA - Field Programmable Gate Array |

| Factory Pack Quantity | 60 | Subcategory | Programmable Logic ICs |

| Total Memory | 106496 bit | Tradename | APEX 20K |

| Part # Aliases | 966782 |

After-Sales- und Abwicklungsbezogen

Zahlung

Zahlung

Bezahlverfahren

Für alternative Zahlungskanäle kontaktieren Sie uns bitte unter:

[email protected] Versand & Verpackung

Versand & Verpackung

Versandart

AVAQ bestimmt und verpackt alle Geräte auf der Grundlage der Schutzanforderungen gegen elektrostatische Entladung (ESD) und Feuchtigkeitsempfindlichkeit (MSL)..

Garantie

Garantie

365-Tage-Produkt

Qualitätsgarantie

Wir versprechen, 365 Tage Qualitätssicherung für alle unsere Produkte zu bieten.

| Menge. | Einzelpreis | Ext. Preis |

|---|---|---|

| 1+ | - | - |

Die unten angegebenen Preise dienen nur als Referenz.