Bezahlverfahren

Compact yet powerful synchronous DRAM solution offering 1MX16 capacity, 6ns speed, CMOS technology, and housed in a PDSO50 package measuring 0

TSOP-50Hersteller:

Herstellerteil #:

HY57V161610DTC-7

Datenblatt:

Paket/Koffer:

TSOP-50

EDA/CAD Modelle:

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for HY57V161610DTC-7, guaranteed quotes back within

[email protected],

or fill below form to Quote for HY57V161610DTC-7, guaranteed quotes back within

![]() 12hr.

12hr.

Bitte füllen Sie das kurze Formular unten aus und wir werden Ihnen umgehend ein Angebot zukommen lassen..

DESCRIPTIONTHE Hyundai HY57V161610D is a 16,777,216-bits CMOS Synchronous DRAM, ideally suited for the main memory and graphic applications which require large memory density and high bandwidth. HY57V161610D is organized as 2banks of 524,288x16. HY57V161610D is offering fully synchronous operation referenced to a positive edge clock. All inputs and outputs are synchronized with the rising edge of the clock input. The data paths are internally pipelined to achieve very high bandwidth. All input and output voltage levels are compatible with LVTTL. Programmable options include the length of pipeline (Read latency of 1,2 or 3), the number of consecutive read or write cycles initiated by a single control command (Burst length of 1,2,4,8 or full page), and the burst count sequence(sequential or interleave). A burst of read or write cycles in progress can be terminated by a burst terminate command or can be interrupted and replaced by a new burst read or write command on any cycle. (This pipeline design is not restricted by a `2N` rule.)FEATURES • Single 3.0V to 3.6V power supply • All device pins are compatible with LVTTL interface • JEDEC standard 400mil 50pin TSOP-II with 0.8mm of pin pitch • All inputs and outputs referenced to positive edge of system clock • Data mask function by UDQM/LDQM • Internal two banks operation • Auto refresh and self refresh • 4096 refresh cycles / 64ms • Programmable Burst Length and Burst Type - 1, 2, 4, 8 and Full Page for Sequence Burst - 1, 2, 4 and 8 for Interleave Burst • Programmable CASLatency ; 1, 2, 3 Clocks

| Product Category | IC Chips |

After-Sales- und Abwicklungsbezogen

Zahlung

Zahlung

Bezahlverfahren

Für alternative Zahlungskanäle kontaktieren Sie uns bitte unter:

[email protected] Versand & Verpackung

Versand & Verpackung

Versandart

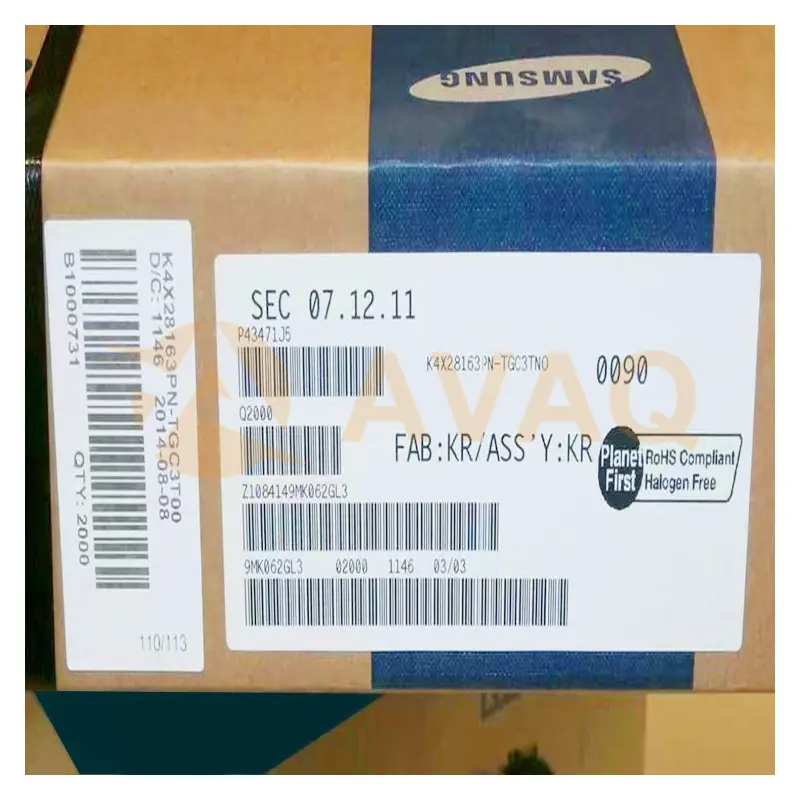

AVAQ bestimmt und verpackt alle Geräte auf der Grundlage der Schutzanforderungen gegen elektrostatische Entladung (ESD) und Feuchtigkeitsempfindlichkeit (MSL)..

Garantie

Garantie

365-Tage-Produkt

Qualitätsgarantie

Wir versprechen, 365 Tage Qualitätssicherung für alle unsere Produkte zu bieten.

| Menge. | Einzelpreis | Ext. Preis |

|---|---|---|

| 1+ | - | - |

Die unten angegebenen Preise dienen nur als Referenz.