Bezahlverfahren

Lead Free Technology

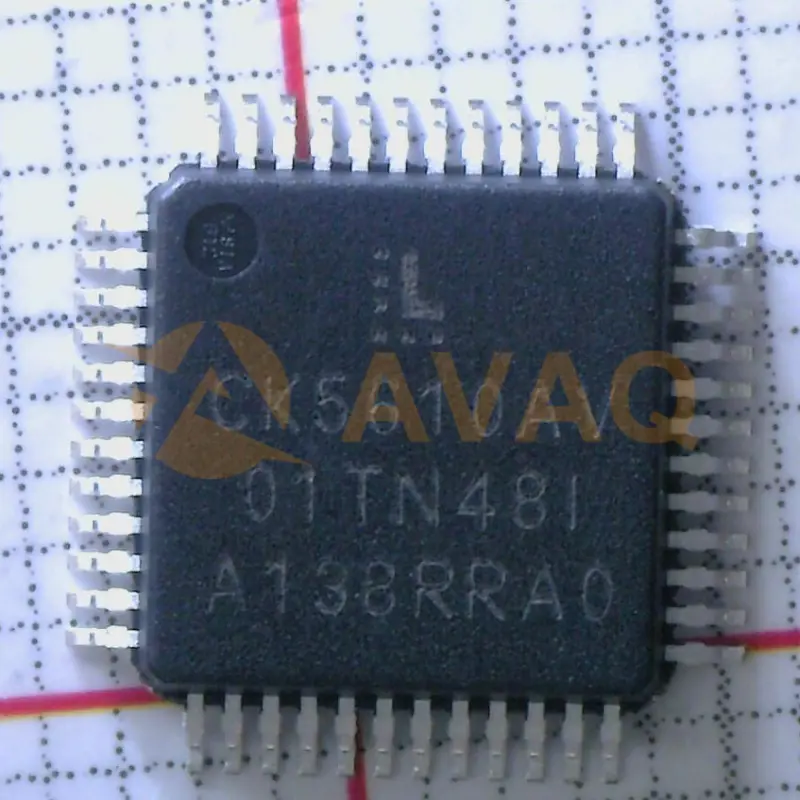

TQFP-48Hersteller:

Lattice Semiconductor Corporation

Herstellerteil #:

ISPPAC-CLK5610AV-01TN48I

Datenblatt:

Pbfree Code:

Yes

Part Life Cycle Code:

Obsolete

Pin Count:

48

Reach Compliance Code:

compliant

EDA/CAD Modelle:

![]() Fordern Sie kostenlose CAD-Modelle für an ISPPAC-CLK5610AV-01TN48I

Fordern Sie kostenlose CAD-Modelle für an ISPPAC-CLK5610AV-01TN48I

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for ISPPAC-CLK5610AV-01TN48I, guaranteed quotes back within

[email protected],

or fill below form to Quote for ISPPAC-CLK5610AV-01TN48I, guaranteed quotes back within

![]() 12hr.

12hr.

Bitte füllen Sie das kurze Formular unten aus und wir werden Ihnen umgehend ein Angebot zukommen lassen..

In addition to its exceptional performance metrics, this IC also comes equipped with programmable features like output dividers and delay control, empowering designers to tailor clock outputs to precise system requirements. The ISPPAC-CLK5610AV-01TN48I operates efficiently on a low power supply voltage, paving the way for energy-efficient solutions in power-sensitive applications. Its compact form factor and high level of integration facilitate seamless integration across a range of electronic devices, making it an ideal choice for networking equipment, communication systems, and industrial automation applications

| Pbfree Code | Yes | Part Life Cycle Code | Obsolete |

| Pin Count | 48 | Reach Compliance Code | compliant |

| HTS Code | 8542.39.00.01 | Family | 5600 |

| Input Conditioning | DIFFERENTIAL | JESD-30 Code | S-PQFP-G48 |

| JESD-609 Code | e3 | Length | 7 mm |

| Logic IC Type | PLL BASED CLOCK DRIVER | Moisture Sensitivity Level | 3 |

| Number of Functions | 1 | Number of Inverted Outputs | |

| Number of Terminals | 48 | Number of True Outputs | 10 |

| Operating Temperature-Max | 85 °C | Operating Temperature-Min | -40 °C |

| Output Characteristics | 3-STATE | Peak Reflow Temperature (Cel) | 260 |

| Propagation Delay (tpd) | 8.8 ns | Qualification Status | Not Qualified |

| Same Edge Skew-Max (tskwd) | 0.05 ns | Seated Height-Max | 1.6 mm |

| Supply Voltage-Max (Vsup) | 3.6 V | Supply Voltage-Min (Vsup) | 3 V |

| Supply Voltage-Nom (Vsup) | 3.3 V | Surface Mount | YES |

| Temperature Grade | INDUSTRIAL | Terminal Finish | MATTE TIN |

| Terminal Form | GULL WING | Terminal Pitch | 0.5 mm |

| Terminal Position | QUAD | Width | 7 mm |

| fmax-Min | 400 MHz | Series | ispClock™ |

| Programmabe | Verified | PLL | Yes with Bypass |

| Input | HSTL, LVCMOS, LVDS, LVPECL, LVTTL, SSTL | Output | EHSTL, HSTL, LVCMOS, LVDS, LVPECL, LVTTL, SSTL |

| Number of Circuits | 1 | Ratio - Input:Output | 1:10 |

| Differential - Input:Output | Yes/Yes | Frequency - Max | 400MHz |

| Divider/Multiplier | Yes/No | Voltage - Supply | 3V ~ 3.6V |

| Operating Temperature | -40°C ~ 85°C | Mounting Type | Surface Mount |

| Base Product Number | ISPPAC-CLK5610A |

After-Sales- und Abwicklungsbezogen

Zahlung

Zahlung

Bezahlverfahren

Für alternative Zahlungskanäle kontaktieren Sie uns bitte unter:

[email protected] Versand & Verpackung

Versand & Verpackung

Versandart

AVAQ bestimmt und verpackt alle Geräte auf der Grundlage der Schutzanforderungen gegen elektrostatische Entladung (ESD) und Feuchtigkeitsempfindlichkeit (MSL)..

Garantie

Garantie

365-Tage-Produkt

Qualitätsgarantie

Wir versprechen, 365 Tage Qualitätssicherung für alle unsere Produkte zu bieten.

| Menge. | Einzelpreis | Ext. Preis |

|---|---|---|

| 1+ | - | - |

Die unten angegebenen Preise dienen nur als Referenz.

AK1573

Asahi Kasei Microdevices/AKM

1000+ $2,489

MN3102

Panasonic

Durable Plastic Package for Moisture-Sensitive Environments

SI5351A-B-GT

Skyworks

Clock Generator Si5351A-B-GT PK

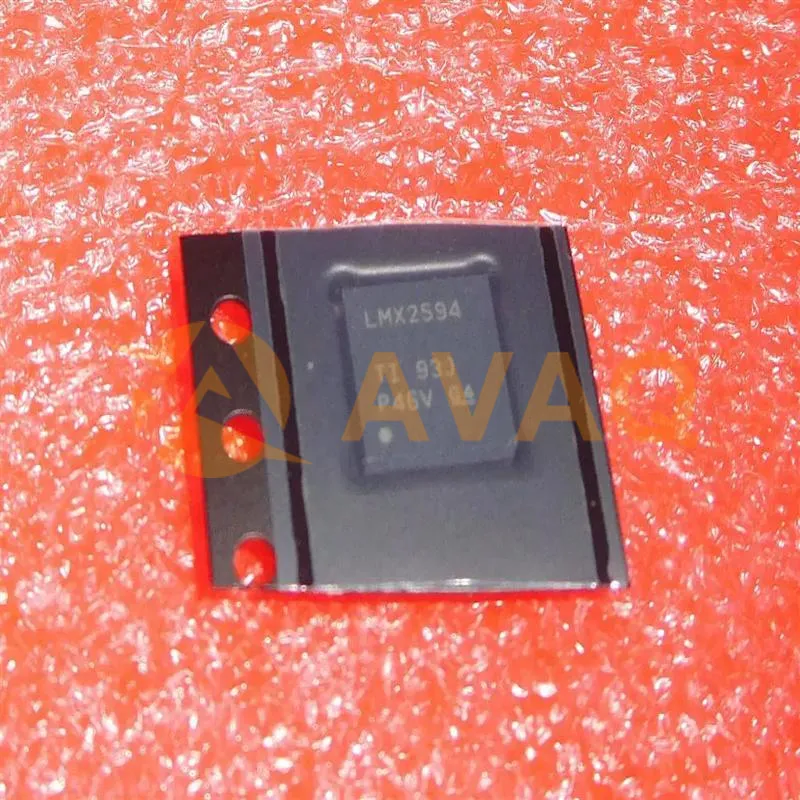

LMX2594RHAT

Texas Instruments

15-GHz wideband PLLatinum™ RF synthesizer with phase synchronization and JESD204B support 40-VQFN -40 to 85"

LM565CN

Texas Instruments

PLL Single 0.25MHz to 0.5MHz 14-Pin MDIP Rail