Bezahlverfahren

Efficient and cost-effective bus controller solutio

QFP208Hersteller:

Lsi Corporation

Herstellerteil #:

LSI53C895A

Datenblatt:

Part Life Cycle Code:

Obsolete

Pin Count:

208

ECCN Code:

3A991.A.2

HTS Code:

8542.31.00.01

EDA/CAD Modelle:

Senden Sie alle Stücklisten an ![]() [email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für LSI53C895A zu erhalten. Garantierte Antwort innerhalb

[email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für LSI53C895A zu erhalten. Garantierte Antwort innerhalb

![]() 12hr.

12hr.

Bitte füllen Sie das kurze Formular unten aus und wir werden Ihnen umgehend ein Angebot zukommen lassen..

| Part Life Cycle Code | Obsolete | Pin Count | 208 |

| ECCN Code | 3A991.A.2 | HTS Code | 8542.31.00.01 |

| Address Bus Width | 32 | Clock Frequency-Max | 40 MHz |

| External Data Bus Width | 32 | JESD-30 Code | S-PQFP-G208 |

| Length | 28 mm | Number of Terminals | 208 |

| Operating Temperature-Max | 70 °C | Qualification Status | Not Qualified |

| Seated Height-Max | 4.1 mm | Supply Voltage-Max | 3.63 V |

| Supply Voltage-Min | 2.97 V | Surface Mount | YES |

| Technology | CMOS | Temperature Grade | COMMERCIAL |

| Terminal Form | GULL WING | Terminal Pitch | 0.5 mm |

| Terminal Position | QUAD | Width | 28 mm |

| uPs/uCs/Peripheral ICs Type | BUS CONTROLLER, SCSI |

After-Sales- und Abwicklungsbezogen

Zahlung

Zahlung

Bezahlverfahren

Für alternative Zahlungskanäle kontaktieren Sie uns bitte unter:

[email protected] Versand & Verpackung

Versand & Verpackung

Versandart

AVAQ bestimmt und verpackt alle Geräte auf der Grundlage der Schutzanforderungen gegen elektrostatische Entladung (ESD) und Feuchtigkeitsempfindlichkeit (MSL)..

Garantie

Garantie

365-Tage-Produkt

Qualitätsgarantie

Wir versprechen, 365 Tage Qualitätssicherung für alle unsere Produkte zu bieten.

| Menge. | Einzelpreis | Ext. Preis |

|---|---|---|

| 1+ | - | - |

Die unten angegebenen Preise dienen nur als Referenz.

CP2102

Silicon Laboratories

Integrate seamlessly into your design with our reliable interface I

MAX232

Texas Instruments

This V device features bps data transfer rates and robust ESD protection

W5500

Wiznet

With its comprehensive set of protocols and interfaces, this IC streamlines network development and deploymen

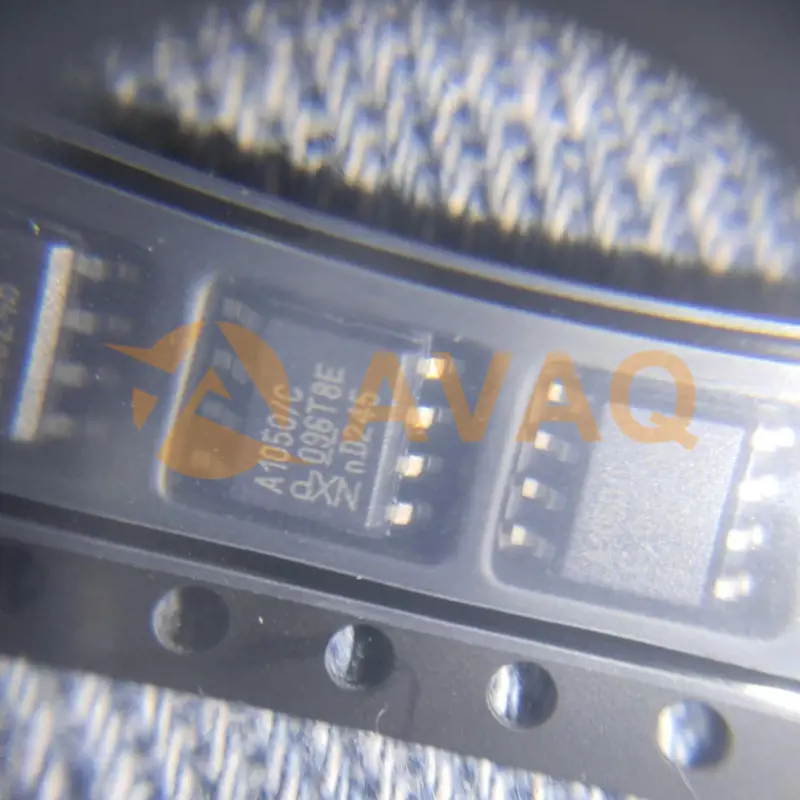

TJA1050

Nxp

Robust and reliable high-speed communication solution for demanding application

RTL2832U

Realtek

High-performance demodulation for DVB-T signals, plug-and-play via US