Bezahlverfahren

Advanced macro cells and gate arrays enable complex system integratio

QFP48Hersteller:

Herstellerteil #:

M4A5-64/32-12VI

Datenblatt:

Pin Count:

44

Released Date:

Mar 22, 2022

Last Modified Date:

Mar 7, 2023 4:10 PM UTC

EDA/CAD Modelle:

Bitte füllen Sie das kurze Formular unten aus und wir werden Ihnen umgehend ein Angebot zukommen lassen..

The ispMACH™ 4A family from Lattice offers an exceptionally flexible architecture and delivers a superior Complex Programmable Logic Device (CPLD) solution of easy-to-use silicon products and software tools. The overall benefits for users are a guaranteed and predictable CPLD solution, faster time-to-market, greater flexibility and lower cost. The ispMACH 4A devices offer densities ranging from 32 to 512 macrocells with 100% utilization and 100% pin-out retention. The ispMACH 4A families offer 5-V (M4A5-xxx) and 3.3-V (M4A3-xxx) operation.

ispMACH 4A products are 5-V or 3.3-V in-system programmable through the JTAG (IEEE Std. 1149.1) interface. JTAG boundary scan testing also allows product testability on automated test equipment for device connectivity.

All ispMACH 4A family members deliver First-Time-Fit and easy system integration with pin-out retention after any design change and refit. For both 3.3-V and 5-V operation, ispMACH 4A products can deliver guaranteed fixed timing as fast as 5.0 ns tPD and 182 MHz fCNT through the SpeedLocking feature when using up to 20 product terms per output.

The ispMACH 4A family offers 20 density-I/O combinations in Thin Quad Flat Pack (TQFP), Plastic Quad Flat Pack (PQFP), Plastic Leaded Chip Carrier (PLCC), Ball Grid Array (BGA), finepitch BGA (fpBGA), and chip-array BGA (caBGA) packages ranging from 44 to 388 pins (Table 3). It also offers I/O safety features for mixed-voltage designs so that the 3.3-V devices can accept 5-V inputs, and 5-V devices do not overdrive 3.3-V inputs. Additional features include BusFriendly inputs and I/Os, a programmable power-down mode for extra power savings and individual output slew rate control for the highest speed transition or for the lowest noise transition.

| Pin Count | 44 | Released Date | Mar 22, 2022 |

| Last Modified Date | Mar 7, 2023 4:10 PM UTC |

After-Sales- und Abwicklungsbezogen

Zahlung

Zahlung

Bezahlverfahren

Für alternative Zahlungskanäle kontaktieren Sie uns bitte unter:

[email protected] Versand & Verpackung

Versand & Verpackung

Versandart

AVAQ bestimmt und verpackt alle Geräte auf der Grundlage der Schutzanforderungen gegen elektrostatische Entladung (ESD) und Feuchtigkeitsempfindlichkeit (MSL)..

Garantie

Garantie

365-Tage-Produkt

Qualitätsgarantie

Wir versprechen, 365 Tage Qualitätssicherung für alle unsere Produkte zu bieten.

| Menge. | Einzelpreis | Ext. Preis |

|---|---|---|

| 1+ | - | - |

Die unten angegebenen Preise dienen nur als Referenz.

Alle Stücklisten (BOM) können per E-Mail gesendet werden an ![]() [email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für M4A5-64/32-12VI zu erstellen, garantierte Angebote zurück innerhalb

[email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für M4A5-64/32-12VI zu erstellen, garantierte Angebote zurück innerhalb

![]() 12 Std.

12 Std.

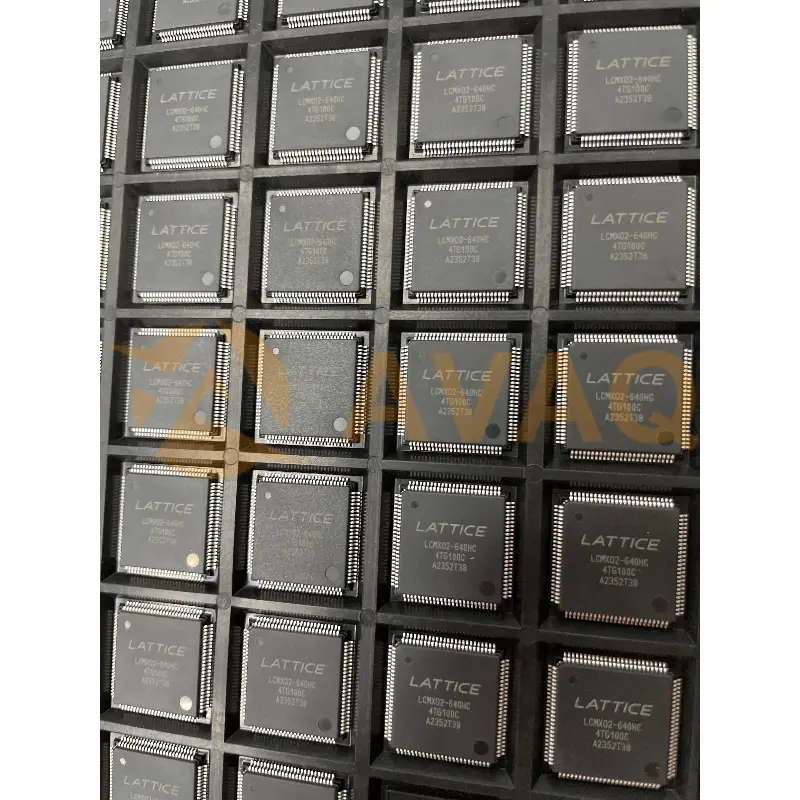

LCMXO2-1200HC-4TG100I

LATTICE

1000+ $3,419

LCMXO2-1200HC-4TG100C

LATTICE

1000+ $2,604

LC4032V-75TN48C

Lattice

High Performance E2 CMOS PLD Generic Array Logic

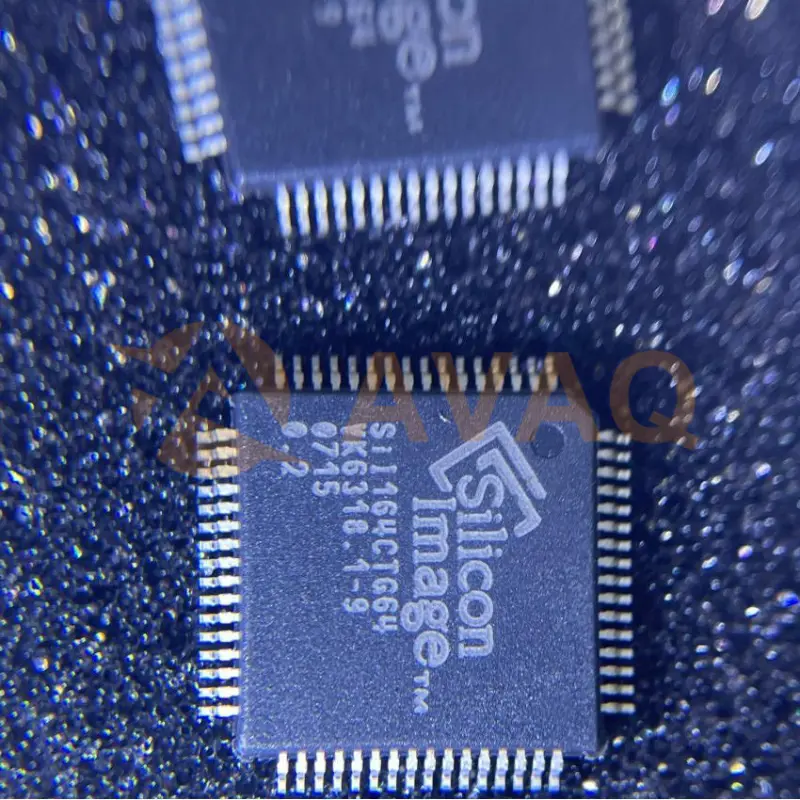

SiI164CTG64

Lattice

TQFP package Transmitter with 2 transmitters

LCMXO2-640HC-4TG100C

Lattice

ROHS Programmable Logic Device (CPLDs/FPGAs) 640 80 TQFP-100(14x14) LCMXO2-640HC-4TG100C