Bezahlverfahren

IC TELECOM INTERFACE 81LBGA

QFPHersteller:

SAA

Herstellerteil #:

PEF2256

Datenblatt:

Series:

FALC™

Function:

Framer, Line Interface Unit (LIU)

Interface:

E1, HDLC, J1, T1

Number Of Circuits:

1

EDA/CAD Modelle:

Senden Sie alle Stücklisten an ![]() [email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für PEF2256 zu erhalten. Garantierte Antwort innerhalb

[email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für PEF2256 zu erhalten. Garantierte Antwort innerhalb

![]() 12hr.

12hr.

Bitte füllen Sie das kurze Formular unten aus und wir werden Ihnen umgehend ein Angebot zukommen lassen..

IntroductionThe FALC®56 framer and line interface component is designed to fulfill all required interfacing between analog E1/T1/J1 lines and the digital PCM system highway, H.100/H.110 or H-MVIP bus for world market telecommunication systems.FeaturesLine Interface• High-density, generic interface for all E1/T1/J1 applications• Analog receive and transmit circuits for long-haul and short-haul applications• E1 or T1/J1 mode selectable• Data and clock recovery using an integrated digital phase-locked loop• Maximum line attenuation up to -43 dB at 1024 kHz (E1) and up to -36 dB at 772 kHz (T1/J1)• Programmable receive equalizer characteristic• Software-selectable receive line termination• Programmable transmit pulse shapes for E1 and T1/J1 pulse masks• Programmable line build-out for CSU signals according to ANSI T1. 403 and FCC68: 0dB, -7.5 dB, -15 dB, -22.5 dB (T1/J1)• Low transmitter output impedances for high transmit return loss• Tristate function of the analog transmit line outputs• Analog switch for redundancy applications• Transmit line monitor protecting the device from damage• Receive line monitor mode• Jitter specifications of ITU-T I.431, G.703, G.736 (E1), G.823 (E1) and AT&T TR62411 (T1/J1) are met• Crystal-less wander and jitter attenuation/compensation• Common master clock reference for E1 and T1/J1 (any frequency within 1.02 and 20 MHz)• Power-down function• Support of automatic protection switching• Dual-rail or single-rail digital inputs and outputs• Unipolar NRZ or CMI for interfacing fiber-optical transmission routes• Selectable line codes (E1: HDB3, AMI/T1: B8ZS, AMI with ZCS)• Loss-of-signal indication with programmable thresholds according to ITU-T G.775, ETS300233 (E1) and ANSI T1.403 (T1/J1)• Optional data stream muting upon LOS detection• Programmable receive slicer threshold• Clock generator for jitter-free system/transmit clocks per channel• Local loop and remote loop for diagnostic purposes• Low power device• Single power supply (3.3 V) or dual power supply (3.3 V and 1.8 V)(Continue .)

| Category | Integrated Circuits (ICs)InterfaceTelecom | Series | FALC™ |

| Function | Framer, Line Interface Unit (LIU) | Interface | E1, HDLC, J1, T1 |

| Number of Circuits | 1 | Voltage - Supply | 1.8V, 3.3V |

| Current - Supply | 80mA | Power (Watts) | 250 mW |

| Operating Temperature | -40°C ~ 85°C | Mounting Type | Surface Mount |

| Base Product Number | PEF 2256 |

After-Sales- und Abwicklungsbezogen

Zahlung

Zahlung

Bezahlverfahren

Für alternative Zahlungskanäle kontaktieren Sie uns bitte unter:

[email protected] Versand & Verpackung

Versand & Verpackung

Versandart

AVAQ bestimmt und verpackt alle Geräte auf der Grundlage der Schutzanforderungen gegen elektrostatische Entladung (ESD) und Feuchtigkeitsempfindlichkeit (MSL)..

Garantie

Garantie

365-Tage-Produkt

Qualitätsgarantie

Wir versprechen, 365 Tage Qualitätssicherung für alle unsere Produkte zu bieten.

| Menge. | Einzelpreis | Ext. Preis |

|---|---|---|

| 1+ | - | - |

Die unten angegebenen Preise dienen nur als Referenz.

NE555

Texas Instruments

100kHz operation frequency with low power consumption for long-lasting performance

CD4017

Onsemi

Compact digital counter for precision measurement application

74LS04

Onsemi

High-quality die for professional use only, unsurfaced and untested

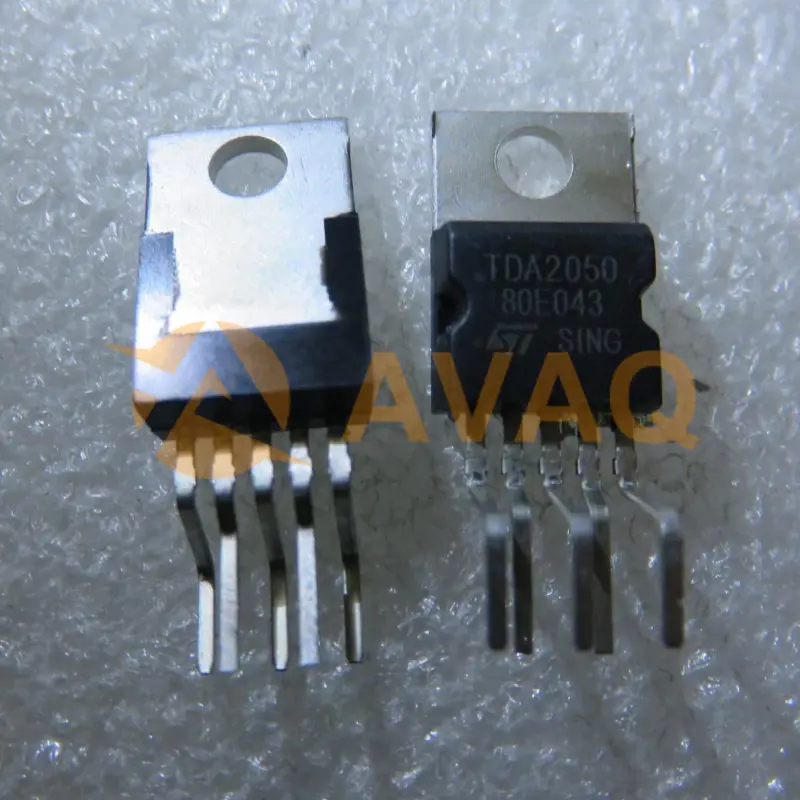

TDA2050

Stmicroelectronics

Effortlessly drives your speakers with crystal-clear sound and robust power

DS1307+

Analog Devices

I2C DIP-8 Real-time Clocks (RTC) ROHS