Bezahlverfahren

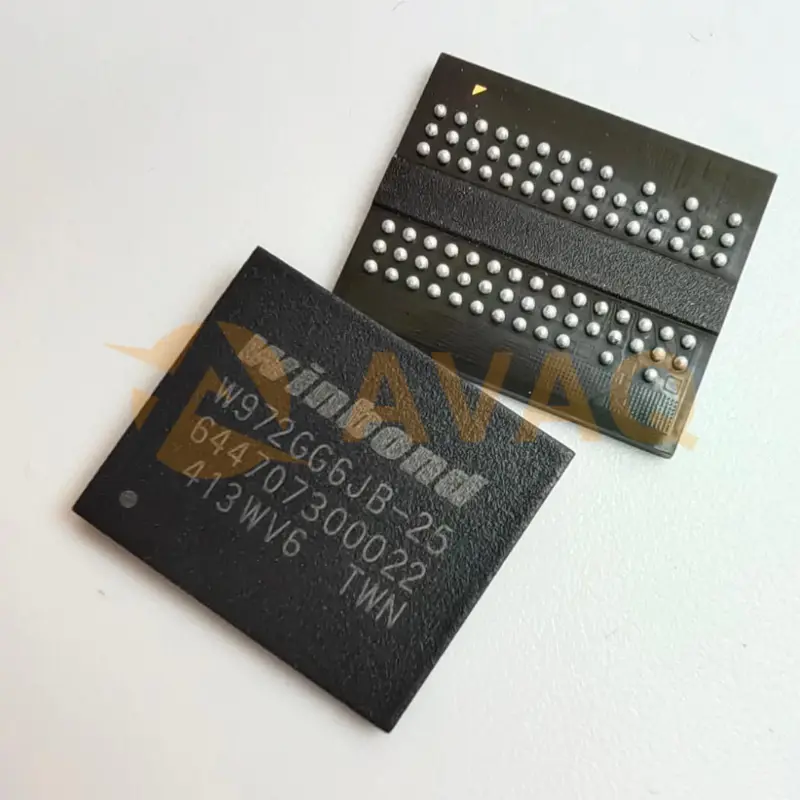

Winbond Electronics Corporation's W972GG6JB-25 product overview

84-WBGA (11x13)Hersteller:

Winbond Electronics

Herstellerteil #:

W972GG6JB-25

Datenblatt:

Part Life Cycle Code:

Obsolete

Reach Compliance Code:

compliant

ECCN Code:

EAR99

HTS Code:

8542.32.00.36

EDA/CAD Modelle:

Bitte füllen Sie das kurze Formular unten aus und wir werden Ihnen umgehend ein Angebot zukommen lassen..

Winbond's W972GG6JB-25 chip is a robust microcontroller designed to meet the demands of modern embedded systems. Its 80MHz operating frequency enables high-speed processing, while the 256KB of flash memory and 32KB of RAM provide ample storage and memory for complex applications. With communication interfaces such as UART, I2C, SPI, and USB, this chip offers versatility and compatibility with a variety of devices. Whether used in industrial automation, consumer electronics, or other applications, the W972GG6JB-25 delivers reliable performance and seamless connectivity

| Part Life Cycle Code | Obsolete | Reach Compliance Code | compliant |

| ECCN Code | EAR99 | HTS Code | 8542.32.00.36 |

| Access Mode | MULTI BANK PAGE BURST | Access Time-Max | 0.4 ns |

| Additional Feature | AUTO/SELF REFRESH | Clock Frequency-Max (fCLK) | 400 MHz |

| I/O Type | COMMON | Interleaved Burst Length | 4,8 |

| JESD-30 Code | R-PBGA-B84 | Length | 13 mm |

| Memory Density | 2147483648 bit | Memory IC Type | DDR2 DRAM |

| Memory Width | 16 | Number of Functions | 1 |

| Number of Ports | 1 | Number of Terminals | 84 |

| Number of Words | 134217728 words | Number of Words Code | 128000000 |

| Operating Mode | SYNCHRONOUS | Operating Temperature-Max | 85 °C |

| Operating Temperature-Min | Organization | 128MX16 | |

| Output Characteristics | 3-STATE | Qualification Status | Not Qualified |

| Refresh Cycles | 8192 | Seated Height-Max | 1.2 mm |

| Self Refresh | YES | Sequential Burst Length | 4,8 |

| Standby Current-Max | 0.012 A | Supply Current-Max | 0.25 mA |

| Supply Voltage-Max (Vsup) | 1.9 V | Supply Voltage-Min (Vsup) | 1.7 V |

| Supply Voltage-Nom (Vsup) | 1.8 V | Surface Mount | YES |

| Technology | CMOS | Temperature Grade | OTHER |

| Terminal Form | BALL | Terminal Pitch | 0.8 mm |

| Terminal Position | BOTTOM | Width | 11 mm |

After-Sales- und Abwicklungsbezogen

Zahlung

Zahlung

Bezahlverfahren

Für alternative Zahlungskanäle kontaktieren Sie uns bitte unter:

[email protected] Versand & Verpackung

Versand & Verpackung

Versandart

AVAQ bestimmt und verpackt alle Geräte auf der Grundlage der Schutzanforderungen gegen elektrostatische Entladung (ESD) und Feuchtigkeitsempfindlichkeit (MSL)..

Garantie

Garantie

365-Tage-Produkt

Qualitätsgarantie

Wir versprechen, 365 Tage Qualitätssicherung für alle unsere Produkte zu bieten.

| Menge. | Einzelpreis | Ext. Preis |

|---|---|---|

| 1+ | - | - |

Die unten angegebenen Preise dienen nur als Referenz.

Alle Stücklisten (BOM) können per E-Mail gesendet werden an ![]() [email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für W972GG6JB-25 zu erstellen, garantierte Angebote zurück innerhalb

[email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für W972GG6JB-25 zu erstellen, garantierte Angebote zurück innerhalb

![]() 12 Std.

12 Std.