Bezahlverfahren

EE PLD, 10ns, 192-Cell, CMOS, PQFP144, LEAD FREE, TQFP-144

TQFP-144Hersteller:

Lattice Semiconductor Corporation

Herstellerteil #:

M4A5-192/96-10VNC

Datenblatt:

Pbfree Code:

Yes

Part Life Cycle Code:

Active

Pin Count:

144

Reach Compliance Code:

compliant

EDA/CAD Modelle:

All bill of materials (BOM) can be sent via email to ![]() [email protected],

or fill below form to Quote for M4A5-192/96-10VNC, guaranteed quotes back within

[email protected],

or fill below form to Quote for M4A5-192/96-10VNC, guaranteed quotes back within

![]() 12hr.

12hr.

Bitte füllen Sie das kurze Formular unten aus und wir werden Ihnen umgehend ein Angebot zukommen lassen..

GENERAL DESCRIPTIONThe ispMACH™ 4A family from Lattice offers an exceptionally flexible architecture and delivers a superior Complex Programmable Logic Device (CPLD) solution of easy-to-use silicon products and software tools. The overall benefits for users are a guaranteed and predictable CPLD solution, faster time-to-market, greater flexibility and lower cost. The ispMACH 4A devices offer densities ranging from 32 to 512 macrocells with 100% utilization and 100% pin-out retention. The ispMACH 4A families offer 5-V (M4A5- xxx) and 3.3-V (M4A3-xxx) operation.

| Pbfree Code | Yes | Part Life Cycle Code | Active |

| Pin Count | 144 | Reach Compliance Code | compliant |

| ECCN Code | EAR99 | HTS Code | 8542.39.00.01 |

| Additional Feature | YES | Clock Frequency-Max | 62.5 MHz |

| In-System Programmable | YES | JESD-30 Code | S-PQFP-G144 |

| JESD-609 Code | e3 | JTAG BST | YES |

| Length | 20 mm | Moisture Sensitivity Level | 3 |

| Number of Dedicated Inputs | 16 | Number of I/O Lines | 96 |

| Number of Macro Cells | 192 | Number of Terminals | 144 |

| Operating Temperature-Max | 70 °C | Operating Temperature-Min | |

| Organization | 16 DEDICATED INPUTS, 96 I/O | Output Function | MACROCELL |

| Peak Reflow Temperature (Cel) | 260 | Programmable Logic Type | EE PLD |

| Propagation Delay | 10 ns | Qualification Status | Not Qualified |

| Seated Height-Max | 1.6 mm | Supply Voltage-Max | 5.25 V |

| Supply Voltage-Min | 4.75 V | Supply Voltage-Nom | 5 V |

| Surface Mount | YES | Technology | CMOS |

| Temperature Grade | COMMERCIAL | Terminal Finish | MATTE TIN |

| Terminal Form | GULL WING | Terminal Pitch | 0.5 mm |

| Terminal Position | QUAD | Time@Peak Reflow Temperature-Max (s) | 40 |

| Width | 20 mm |

After-Sales- und Abwicklungsbezogen

Zahlung

Zahlung

Bezahlverfahren

Für alternative Zahlungskanäle kontaktieren Sie uns bitte unter:

[email protected] Versand & Verpackung

Versand & Verpackung

Versandart

AVAQ bestimmt und verpackt alle Geräte auf der Grundlage der Schutzanforderungen gegen elektrostatische Entladung (ESD) und Feuchtigkeitsempfindlichkeit (MSL)..

Garantie

Garantie

365-Tage-Produkt

Qualitätsgarantie

Wir versprechen, 365 Tage Qualitätssicherung für alle unsere Produkte zu bieten.

| Menge. | Einzelpreis | Ext. Preis |

|---|---|---|

| 1+ | - | - |

Die unten angegebenen Preise dienen nur als Referenz.

C100

Issi

Video ICs 4MP H.265 Video Processor - 64MB DDR2, BGA85, 5mm x 6mm

NE555

Texas Instruments

100kHz operation frequency with low power consumption for long-lasting performance

CD4017

Onsemi

Compact digital counter for precision measurement application

74LS04

Onsemi

High-quality die for professional use only, unsurfaced and untested

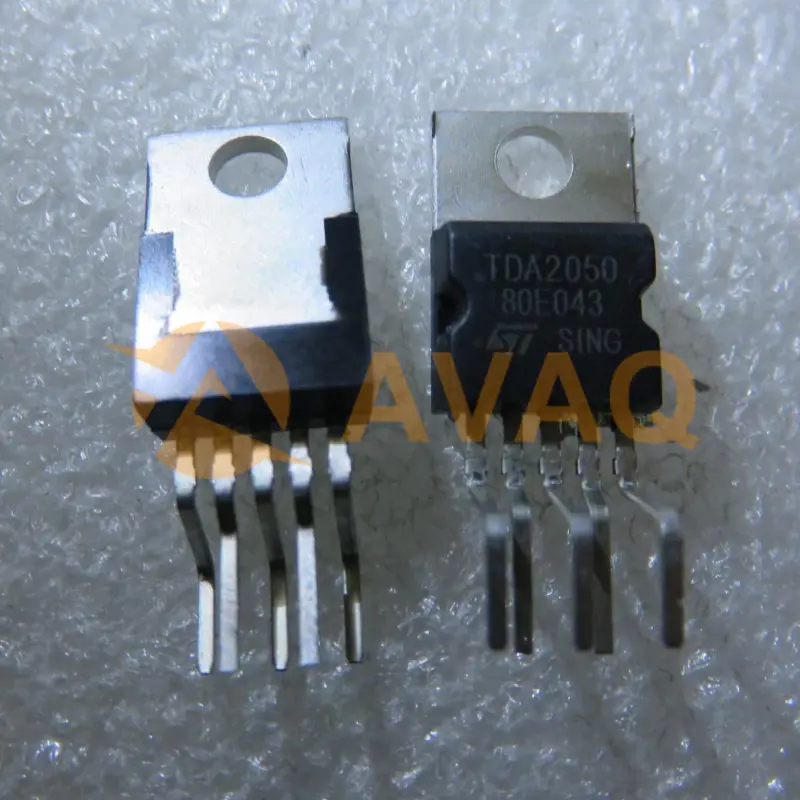

TDA2050

Stmicroelectronics

Effortlessly drives your speakers with crystal-clear sound and robust power