Bezahlverfahren

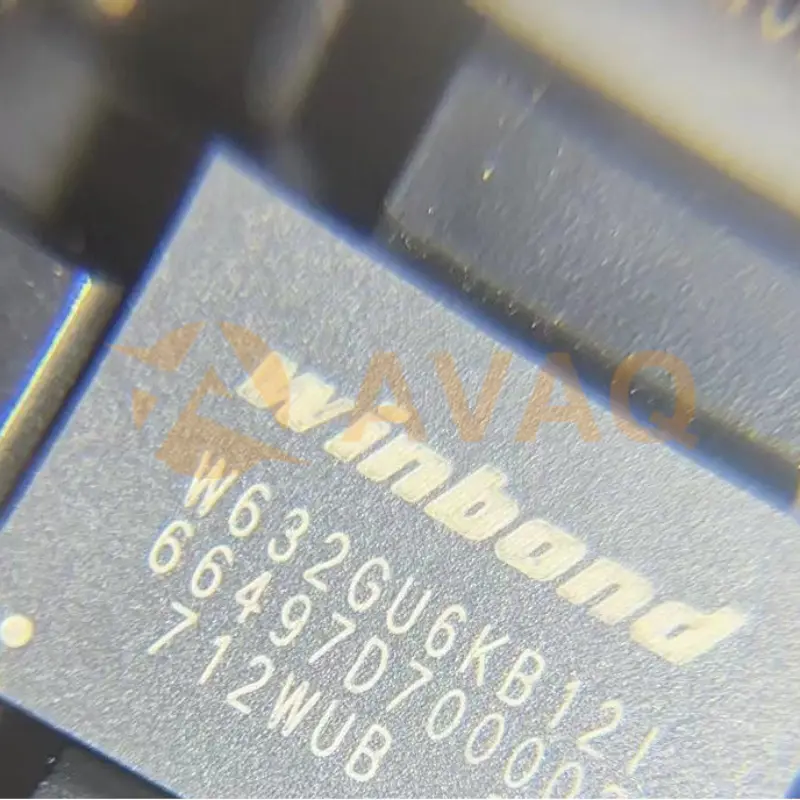

2Gbit DDR3L SDRAM

96-WBGA (9x13)Hersteller:

Winbond Electronics

Herstellerteil #:

W632GU6KB12I

Datenblatt:

Part Life Cycle Code:

Active

Pin Count:

96

Reach Compliance Code:

compliant

ECCN Code:

EAR99

EDA/CAD Modelle:

Bitte füllen Sie das kurze Formular unten aus und wir werden Ihnen umgehend ein Angebot zukommen lassen..

Automotive manufacturers looking to enhance the performance of their onboard systems can trust the W632GU6KB12I chip to deliver reliable and fast data storage capabilities. Its DDR4 SDRAM technology ensures quick access to critical information, while the low-power design helps conserve energy without compromising on speed or capacity. Whether it's for infotainment systems, navigation tools, or advanced sensor networks, this memory chip excels in demanding automotive applications where quality and efficiency are paramount

| Part Life Cycle Code | Active | Pin Count | 96 |

| Reach Compliance Code | compliant | ECCN Code | EAR99 |

| HTS Code | 8542.32.00.36 | Access Mode | MULTI BANK PAGE BURST |

| Additional Feature | AUTO/SELF REFRESH | I/O Type | COMMON |

| Interleaved Burst Length | 8 | JESD-30 Code | R-PBGA-B96 |

| Memory IC Type | DDR3L DRAM | Memory Organization | 128MX16 |

| Memory Width | 16 | Number of Functions | 1 |

| Number of Ports | 1 | Number of Terminals | 96 |

| Number of Words Code | 128000000 | Operating Mode | SYNCHRONOUS |

| Output Characteristics | 3-STATE | Peak Reflow Temperature (Cel) | NOT SPECIFIED |

| Refresh Cycles | 8192 | Self Refresh | YES |

| Sequential Burst Length | 8 | Surface Mount | YES |

| Technology | CMOS | Temperature Grade | INDUSTRIAL |

| Terminal Form | BALL | Terminal Position | BOTTOM |

| Time@Peak Reflow Temperature-Max (s) | NOT SPECIFIED |

After-Sales- und Abwicklungsbezogen

Zahlung

Zahlung

Bezahlverfahren

Für alternative Zahlungskanäle kontaktieren Sie uns bitte unter:

[email protected] Versand & Verpackung

Versand & Verpackung

Versandart

AVAQ bestimmt und verpackt alle Geräte auf der Grundlage der Schutzanforderungen gegen elektrostatische Entladung (ESD) und Feuchtigkeitsempfindlichkeit (MSL)..

Garantie

Garantie

365-Tage-Produkt

Qualitätsgarantie

Wir versprechen, 365 Tage Qualitätssicherung für alle unsere Produkte zu bieten.

| Menge. | Einzelpreis | Ext. Preis |

|---|---|---|

| 1+ | - | - |

Die unten angegebenen Preise dienen nur als Referenz.

Alle Stücklisten (BOM) können per E-Mail gesendet werden an ![]() [email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für W632GU6KB12I zu erstellen, garantierte Angebote zurück innerhalb

[email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für W632GU6KB12I zu erstellen, garantierte Angebote zurück innerhalb

![]() 12 Std.

12 Std.