Bezahlverfahren

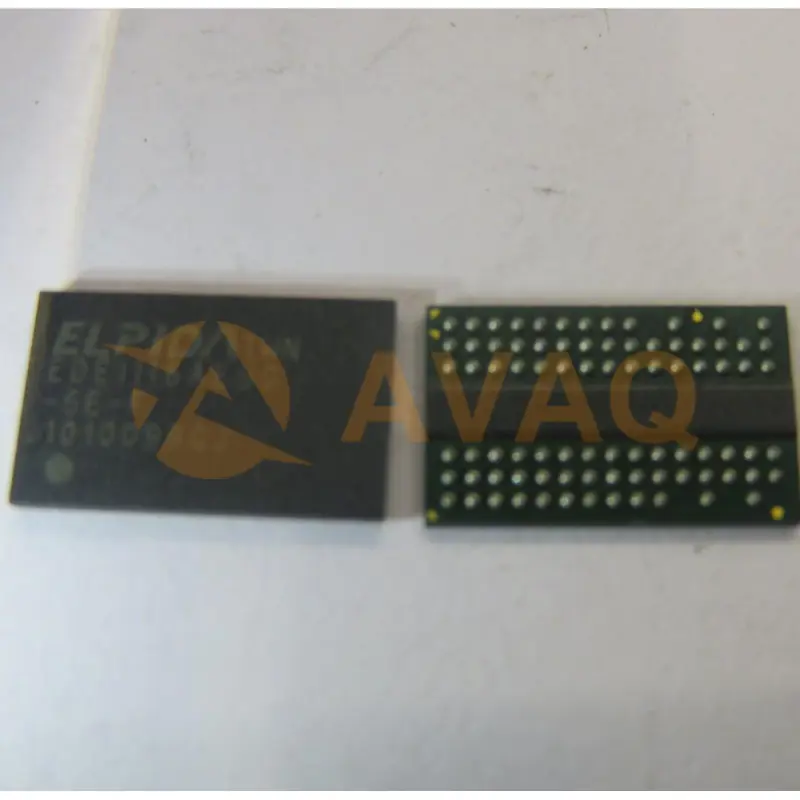

DDR DRAM, 64MX16, 0.45ns, CMOS, PBGA84, HALOGEN FREE AND ROHS COMPLIANT, FBGA-84

BGAHersteller:

ELPIDA

Herstellerteil #:

EDE1116AEBG-6E-F

Datenblatt:

Paket/Koffer:

BGA

Produktart:

EDA/CAD Modelle:

Senden Sie alle Stücklisten an ![]() [email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für EDE1116AEBG-6E-F zu erhalten. Garantierte Antwort innerhalb

[email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für EDE1116AEBG-6E-F zu erhalten. Garantierte Antwort innerhalb

![]() 12hr.

12hr.

Bitte füllen Sie das kurze Formular unten aus und wir werden Ihnen umgehend ein Angebot zukommen lassen..

Double-data-rate architecture; two data transfers per clock cycle

The high-speed data transfer is realized by the 4 bits prefetch pipelined architecture

Bi-directional differential data strobe (DQS and /DQS) is transmitted/received with data for capturing data at the receiver

DQS is edge-aligned with data for READs; center aligned with data for WRITEs

Differential clock inputs (CK and /CK)

DLL aligns DQ and DQS transitions with CK transitions

Commands entered on each positive CK edge; data and data mask referenced to both edges of DQS

Data mask (DM) for write data

Posted /CAS by programmable additive latency for better command and data bus efficiency

Programmable RDQS, /RDQS output for making 8 organization compatible to 4 organization

/DQS, (/RDQS) can be disabled for single-ended Data Strobe operation

Off-Chip Driver (OCD) impedance adjustment is not supported.

| Product Category | Memory ICs |

After-Sales- und Abwicklungsbezogen

Zahlung

Zahlung

Bezahlverfahren

Für alternative Zahlungskanäle kontaktieren Sie uns bitte unter:

[email protected] Versand & Verpackung

Versand & Verpackung

Versandart

AVAQ bestimmt und verpackt alle Geräte auf der Grundlage der Schutzanforderungen gegen elektrostatische Entladung (ESD) und Feuchtigkeitsempfindlichkeit (MSL)..

Garantie

Garantie

365-Tage-Produkt

Qualitätsgarantie

Wir versprechen, 365 Tage Qualitätssicherung für alle unsere Produkte zu bieten.

| Menge. | Einzelpreis | Ext. Preis |

|---|---|---|

| 1+ | - | - |

Die unten angegebenen Preise dienen nur als Referenz.