Bezahlverfahren

FBGA

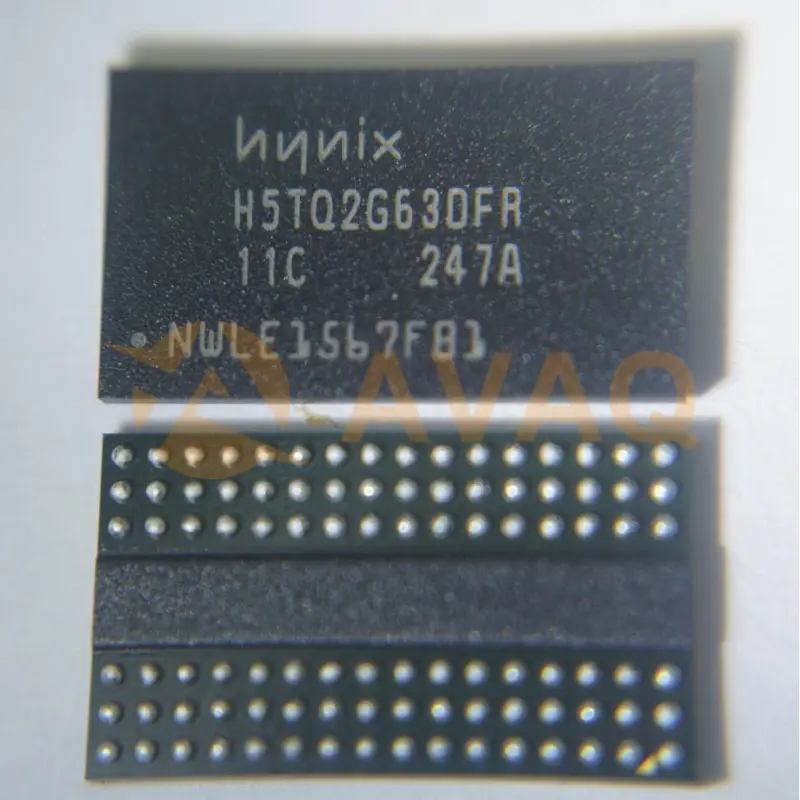

Hersteller:

SKHYNIX

Herstellerteil #:

H5TQ2G63DFR-11C

Datenblatt:

Paket/Koffer:

FBGA

Produktart:

EDA/CAD Modelle:

Senden Sie alle Stücklisten an ![]() [email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für H5TQ2G63DFR-11C zu erhalten. Garantierte Antwort innerhalb

[email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für H5TQ2G63DFR-11C zu erhalten. Garantierte Antwort innerhalb

![]() 12hr.

12hr.

Bitte füllen Sie das kurze Formular unten aus und wir werden Ihnen umgehend ein Angebot zukommen lassen..

VDD=VDDQ=1.5V +/- 0.075V

Fully differential clock inputs (CK, CK) operation

Differential Data Strobe (DQS, DQS)

On chip DLL align DQ, DQS and DQS transition with CK

transition

DM masks write data-in at the both rising and falling

edges of the data strobe

All addresses and control inputs except data,

data strobes and data masks latched on the

rising edges of the clock

Programmable CAS latency 5, 6, 7, 8, 9, 10, 11, 12, 13

and 14 supported

Programmable additive latency 0, CL-1, and CL-2

supported

Programmable CAS Write latency (CWL) = 5, 6, 7, 8, 9, 10

Programmable burst length 4/8 with both nibble

sequential and interleave mode

BL switch on the fly

8banks

Average Refresh Cycle (Tcase of0 oC~ 95oC)

- 7.8 s at 0oC ~ 85 oC

- 3.9 s at 85oC ~ 95 oC

JEDEC standard 78ball FBGA(x4/x8)

Driver strength selected by EMRS

Dynamic On Die Termination supported

Asynchronous RESET pin supported

ZQ calibration supported

TDQS (Termination Data Strobe) supported (x8 only)

Write Levelization supported

8 bit pre-fetch

This product in compliance with the RoHS directive.

| Product Category | Memory ICs |

After-Sales- und Abwicklungsbezogen

Zahlung

Zahlung

Bezahlverfahren

Für alternative Zahlungskanäle kontaktieren Sie uns bitte unter:

[email protected] Versand & Verpackung

Versand & Verpackung

Versandart

AVAQ bestimmt und verpackt alle Geräte auf der Grundlage der Schutzanforderungen gegen elektrostatische Entladung (ESD) und Feuchtigkeitsempfindlichkeit (MSL)..

Garantie

Garantie

365-Tage-Produkt

Qualitätsgarantie

Wir versprechen, 365 Tage Qualitätssicherung für alle unsere Produkte zu bieten.

| Menge. | Einzelpreis | Ext. Preis |

|---|---|---|

| 1+ | - | - |

Die unten angegebenen Preise dienen nur als Referenz.