Bezahlverfahren

LCMXO2-1200HC-6SG32I is an FPGA (Field Programmable Gate Array) from the MachXO2 series, featuring 1280 LUTs and supporting voltages of 2.5/3.3V

QFN-32Hersteller:

Herstellerteil #:

LCMXO2-1200HC-6SG32I

Datenblatt:

Part Life Cycle Code:

Active

Reach Compliance Code:

compliant

ECCN Code:

EAR99

HTS Code:

8542.39.00.01

EDA/CAD Modelle:

![]() Fordern Sie kostenlose CAD-Modelle für an LCMXO2-1200HC-6SG32I

Fordern Sie kostenlose CAD-Modelle für an LCMXO2-1200HC-6SG32I

Senden Sie alle Stücklisten an ![]() [email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für LCMXO2-1200HC-6SG32I zu erhalten. Garantierte Antwort innerhalb

[email protected],

oder füllen Sie das untenstehende Formular aus, um ein Angebot für LCMXO2-1200HC-6SG32I zu erhalten. Garantierte Antwort innerhalb

![]() 12hr.

12hr.

Bitte füllen Sie das kurze Formular unten aus und wir werden Ihnen umgehend ein Angebot zukommen lassen..

Lattice Semiconductor's LCMXO2-1200HC-6SG32I is a member of the XO2 family of FPGAs and is known for its high logic capacity, low power consumption, and impressive performance. Featuring 1200 Look-Up Tables for logic implementation and 32 I/O pins, this FPGA is designed to meet the demands of today's technology-driven world. Its Speed Grade designation and High Capacity status further highlight its suitability for various applications, from mobile devices to industrial automation systems

| Part Life Cycle Code | Active | Reach Compliance Code | compliant |

| ECCN Code | EAR99 | HTS Code | 8542.39.00.01 |

| Date Of Intro | 2016-03-11 | Additional Feature | ALSO OPERATES AT 3.3 V NOMINAL SUPPLY |

| JESD-30 Code | S-XQCC-N32 | Length | 5 mm |

| Moisture Sensitivity Level | 1 | Number of CLBs | 160 |

| Number of Inputs | 21 | Number of Logic Cells | 1280 |

| Number of Outputs | 21 | Number of Terminals | 32 |

| Operating Temperature-Max | 100 °C | Operating Temperature-Min | -40 °C |

| Organization | 160 CLBS | Packing Method | TRAY |

| Peak Reflow Temperature (Cel) | 260 | Programmable Logic Type | FIELD PROGRAMMABLE GATE ARRAY |

| Seated Height-Max | 1 mm | Supply Voltage-Max | 3.6 V |

| Supply Voltage-Min | 2.375 V | Supply Voltage-Nom | 2.5 V |

| Surface Mount | YES | Temperature Grade | INDUSTRIAL |

| Terminal Form | NO LEAD | Terminal Pitch | 0.5 mm |

| Terminal Position | QUAD | Time@Peak Reflow Temperature-Max (s) | NOT SPECIFIED |

| Width | 5 mm |

After-Sales- und Abwicklungsbezogen

Zahlung

Zahlung

Bezahlverfahren

Für alternative Zahlungskanäle kontaktieren Sie uns bitte unter:

[email protected] Versand & Verpackung

Versand & Verpackung

Versandart

AVAQ bestimmt und verpackt alle Geräte auf der Grundlage der Schutzanforderungen gegen elektrostatische Entladung (ESD) und Feuchtigkeitsempfindlichkeit (MSL)..

Garantie

Garantie

365-Tage-Produkt

Qualitätsgarantie

Wir versprechen, 365 Tage Qualitätssicherung für alle unsere Produkte zu bieten.

| Menge. | Einzelpreis | Ext. Preis |

|---|---|---|

| 1+ | - | - |

Die unten angegebenen Preise dienen nur als Referenz.

LCMXO2-1200HC-4TG100I

LATTICE

1000+ $3,419

LCMXO2-1200HC-4TG100C

LATTICE

1000+ $2,604

LC4032V-75TN48C

Lattice

High Performance E2 CMOS PLD Generic Array Logic

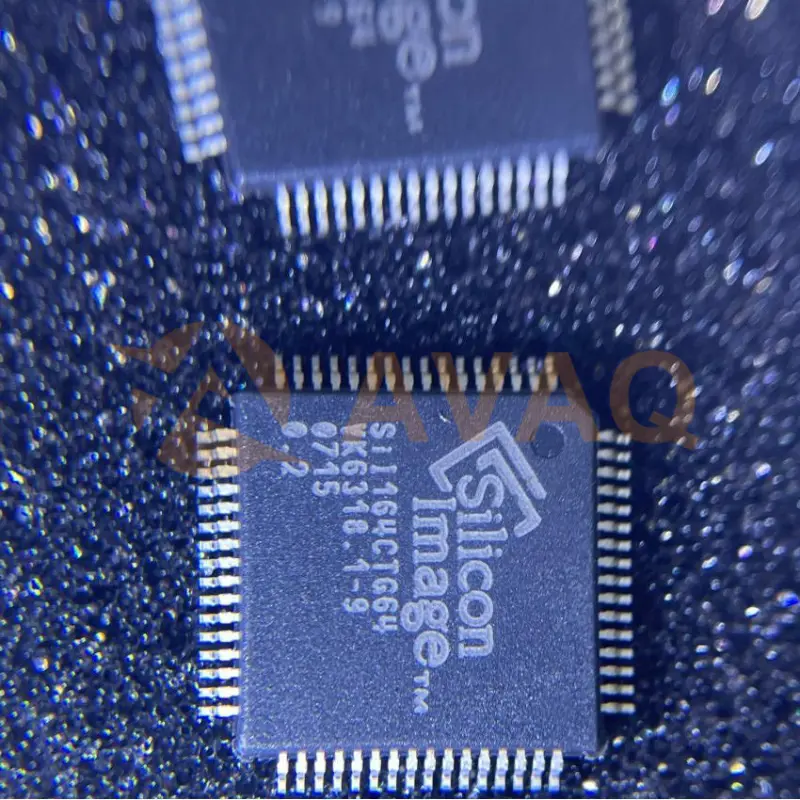

SiI164CTG64

Lattice

TQFP package Transmitter with 2 transmitters

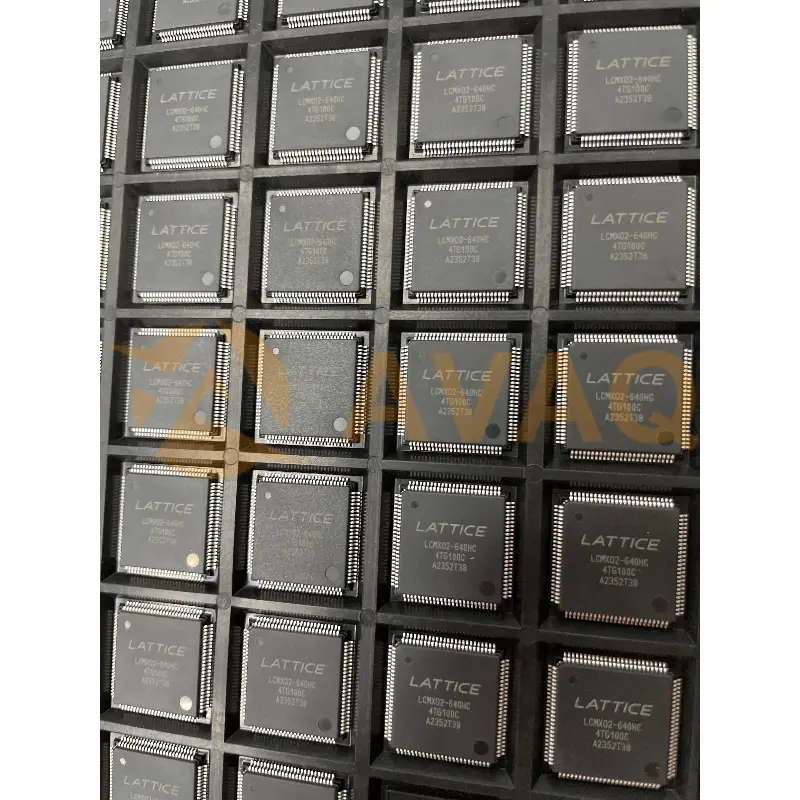

LCMXO2-640HC-4TG100C

Lattice

ROHS Programmable Logic Device (CPLDs/FPGAs) 640 80 TQFP-100(14x14) LCMXO2-640HC-4TG100C